Today is: Tuesday May 19, 2026

This site contains information on measurement results from my Master's Thesis Measurement Board design.

-

Sine Wave @ 30MHz; Time Domain

-

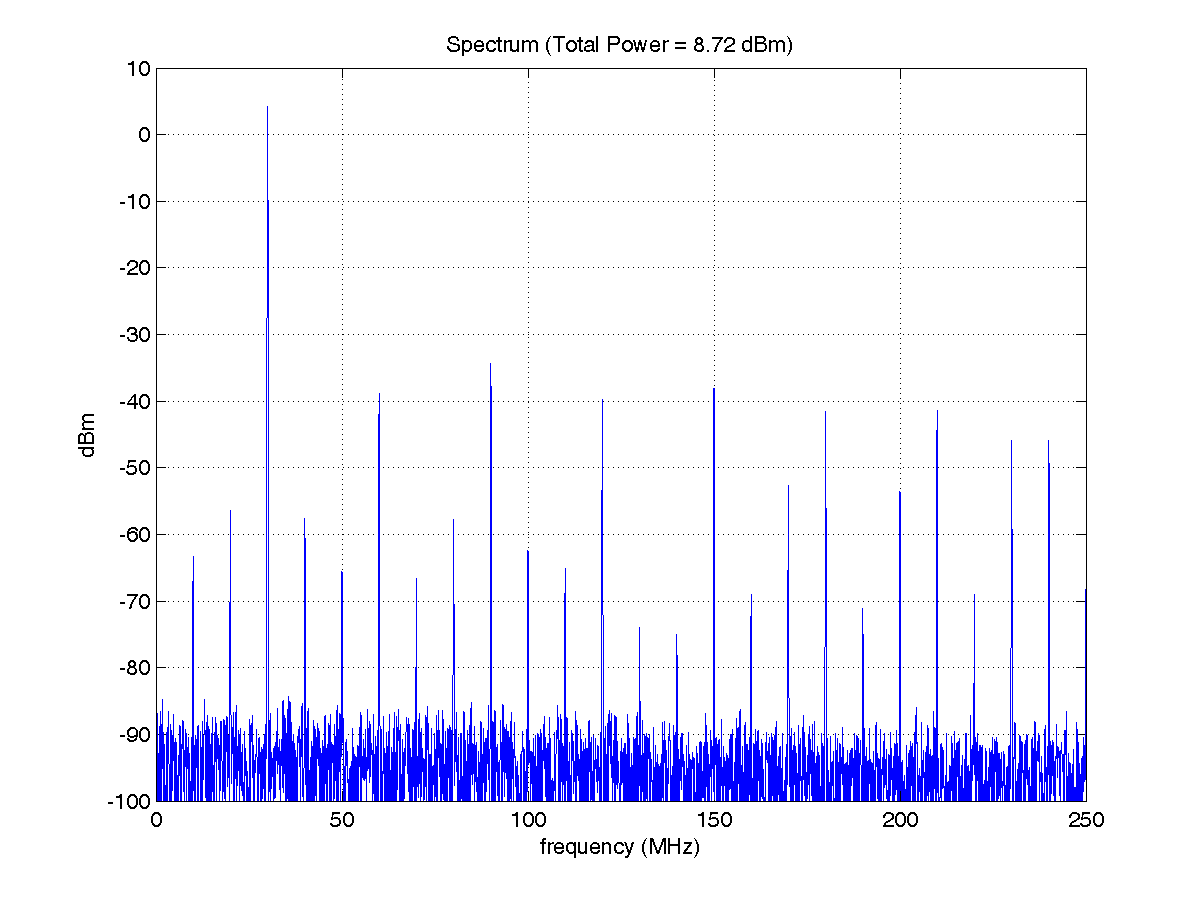

Sine Wave @ 30MHz; Frequency Domain; Spurs are due to Signal Clipping at ADC Input.

-

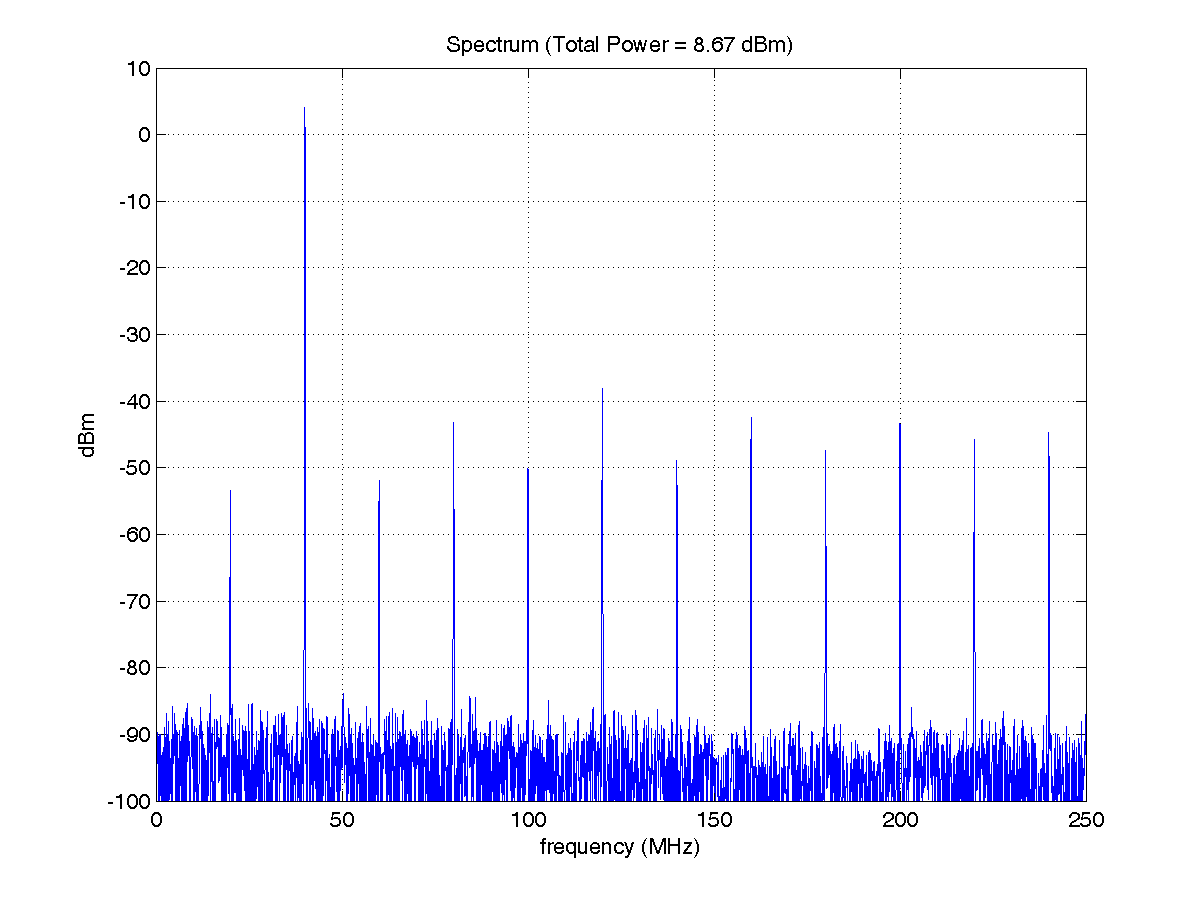

Sine Wave @ 30MHz; Decimated by 8; Frequency Domain; Spurs are due to Signal Clipping at ADC Input.

-

Sine Wave @ 30MHz; Time Domain; ADC Data on top of DAC Data

-

Sine Wave @ 40MHz; Time Domain

-

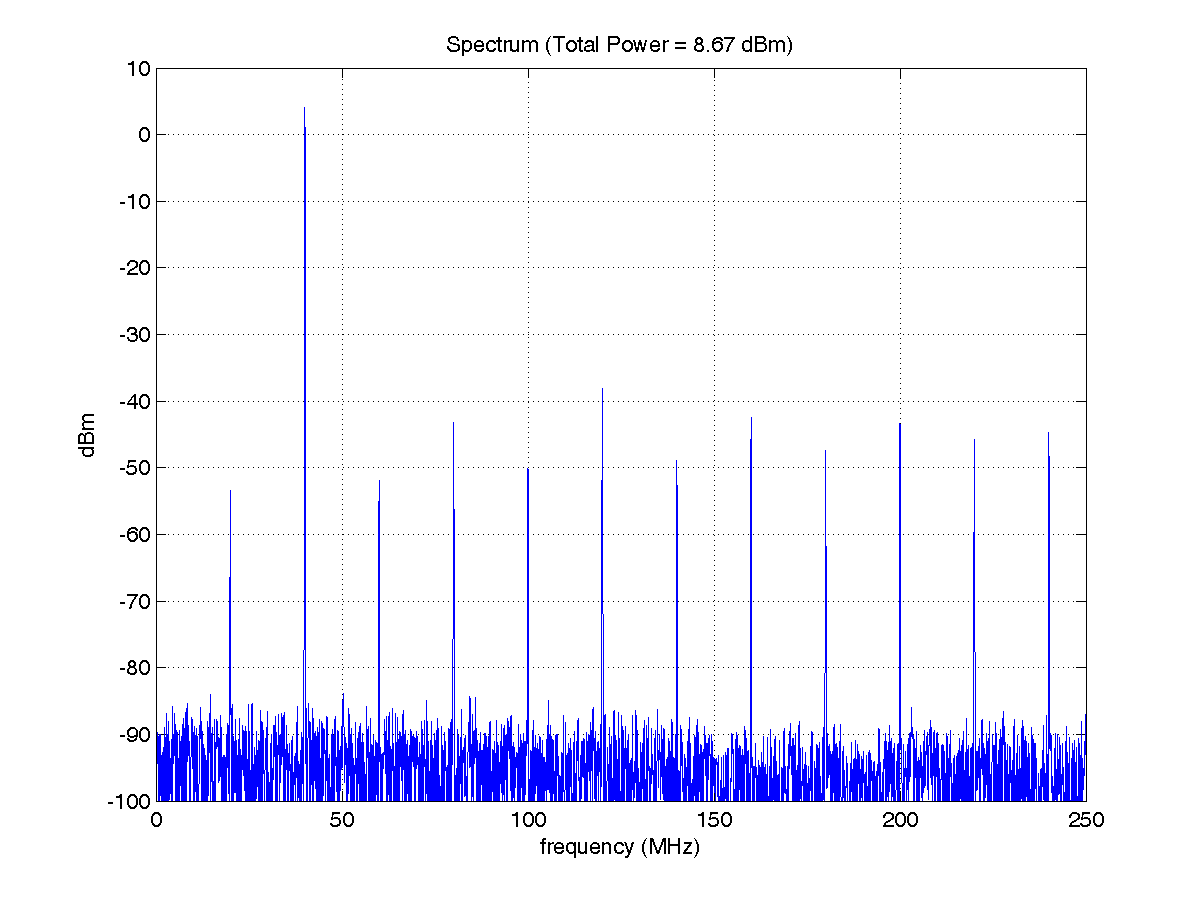

Sine Wave @ 40MHz; Frequency Domain; Spurs are due to Signal Clipping at ADC Input.

-

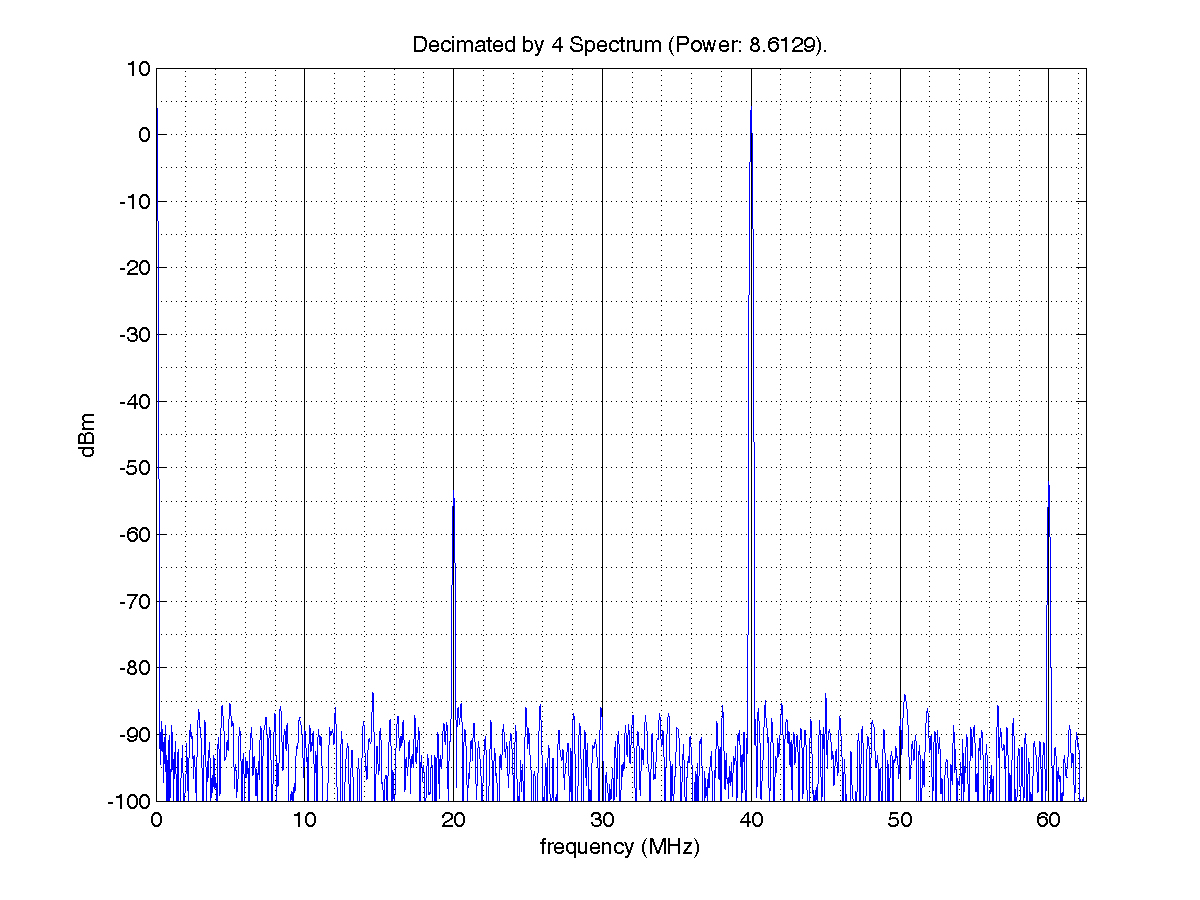

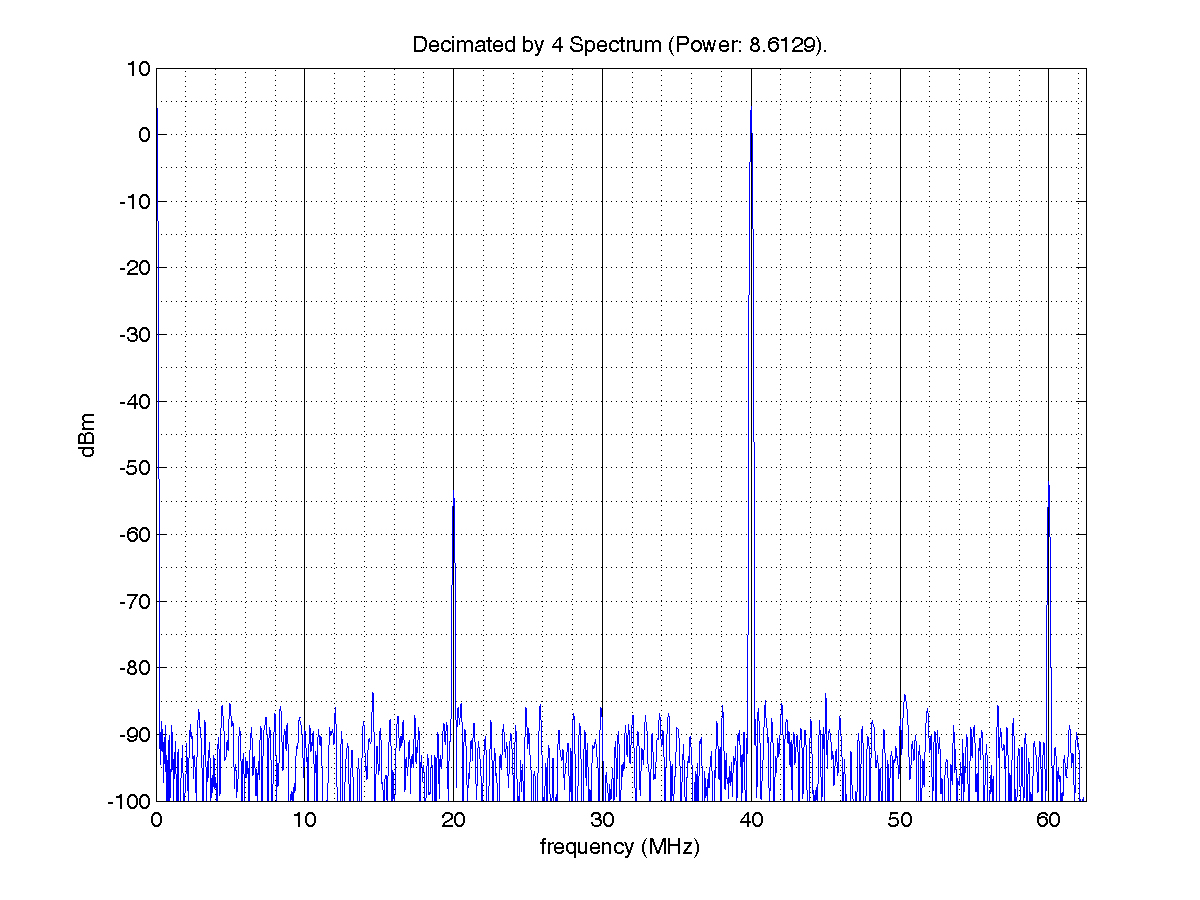

Sine Wave @ 40MHz; Decimated by 4; Frequency Domain; Spurs are due to Signal Clipping at ADC Input.

-

Sine Wave @ 40MHz; Time Domain; ADC Data on top of DAC Data

-

Sine Wave @ 80MHz; Time Domain

-

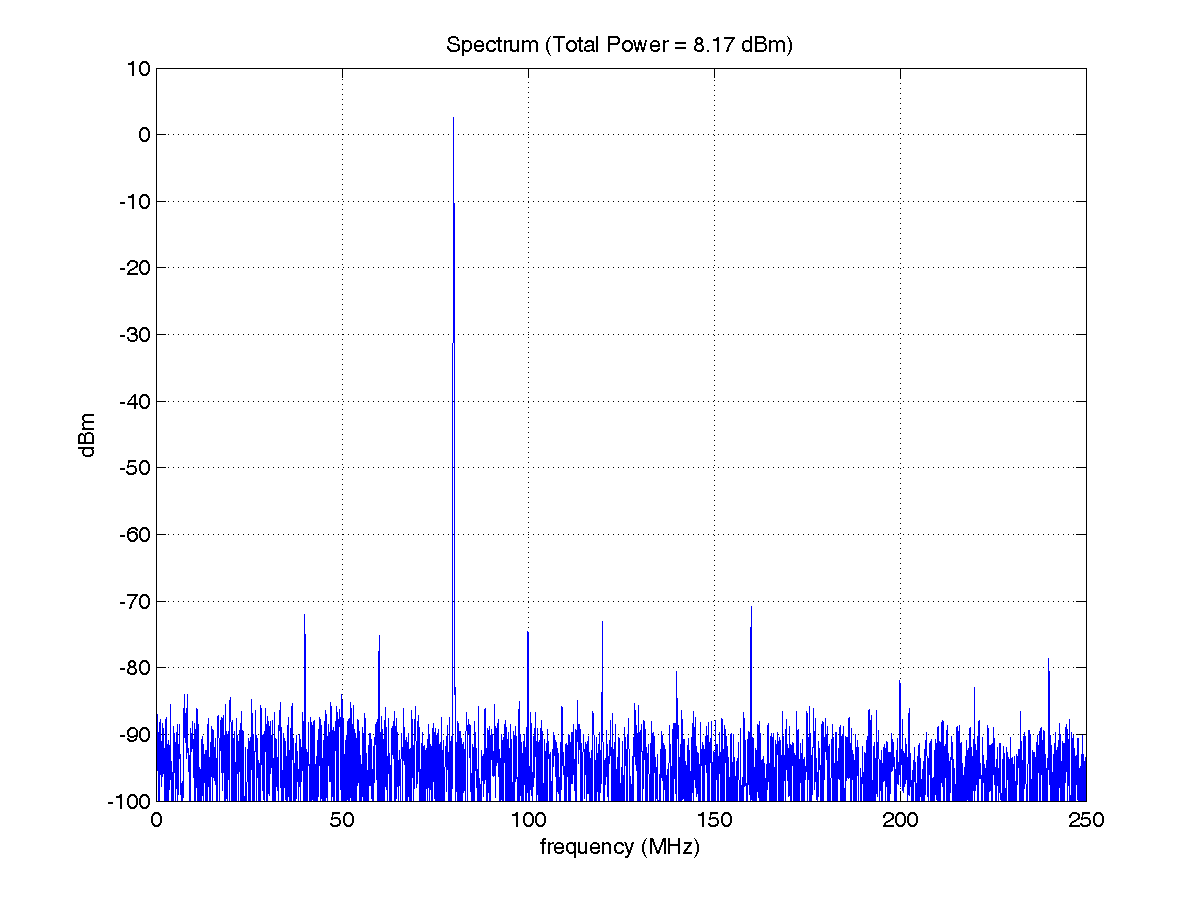

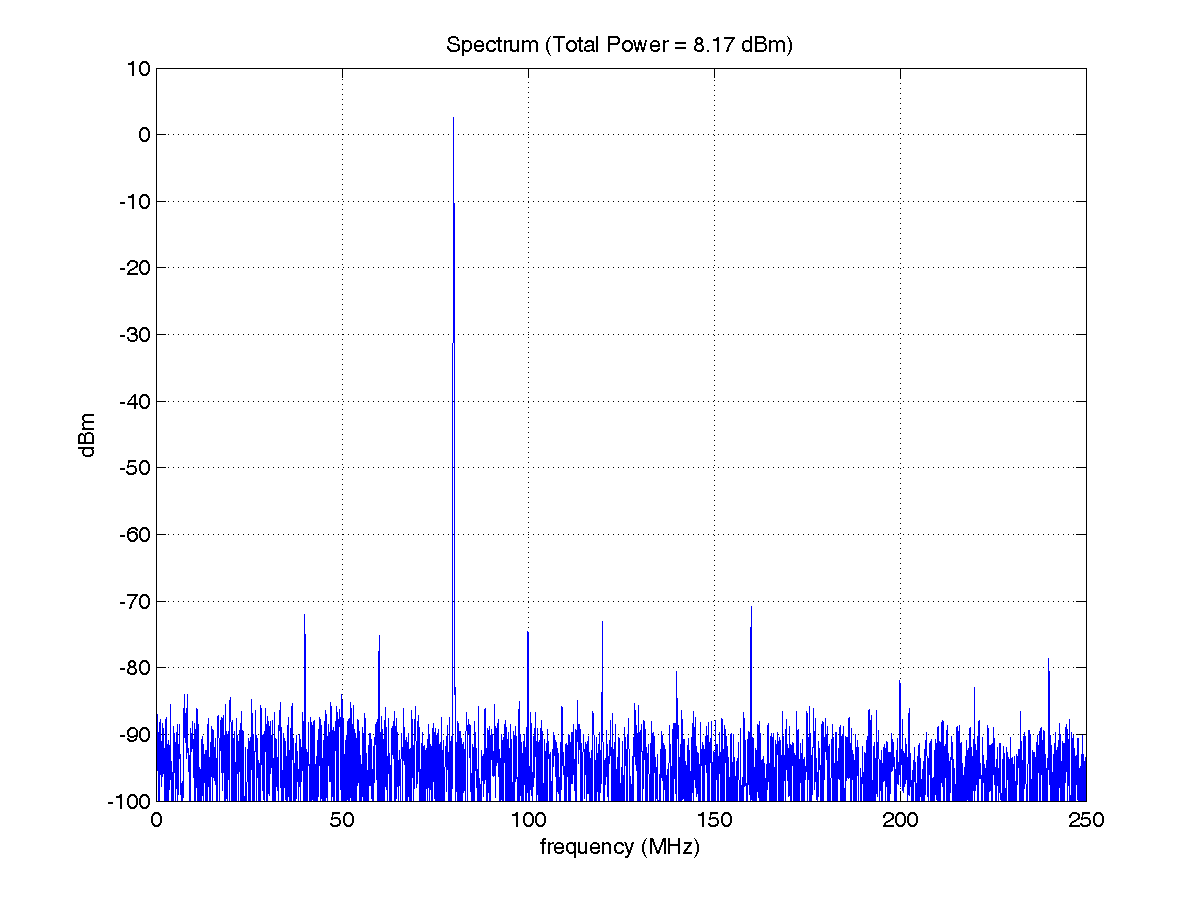

Sine Wave @ 80MHz; Frequency Domain

-

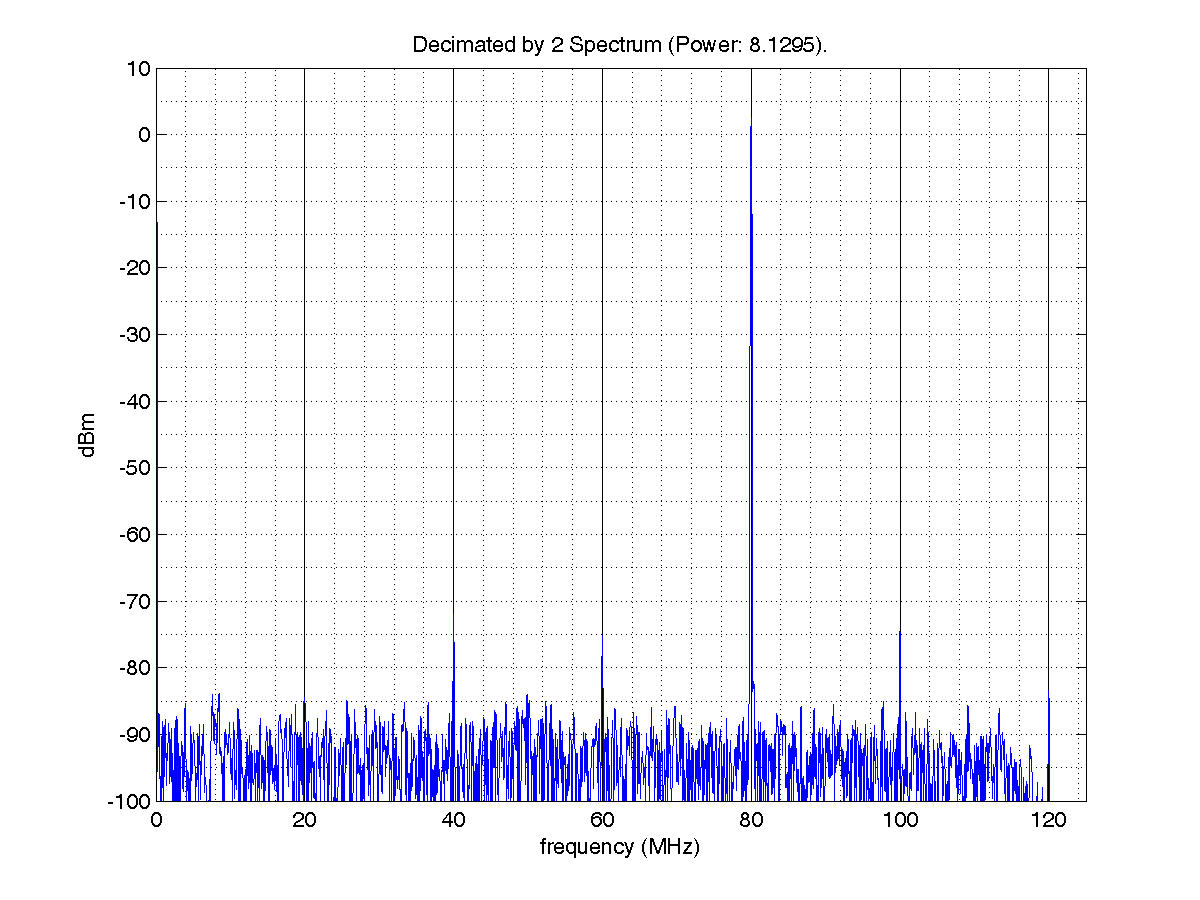

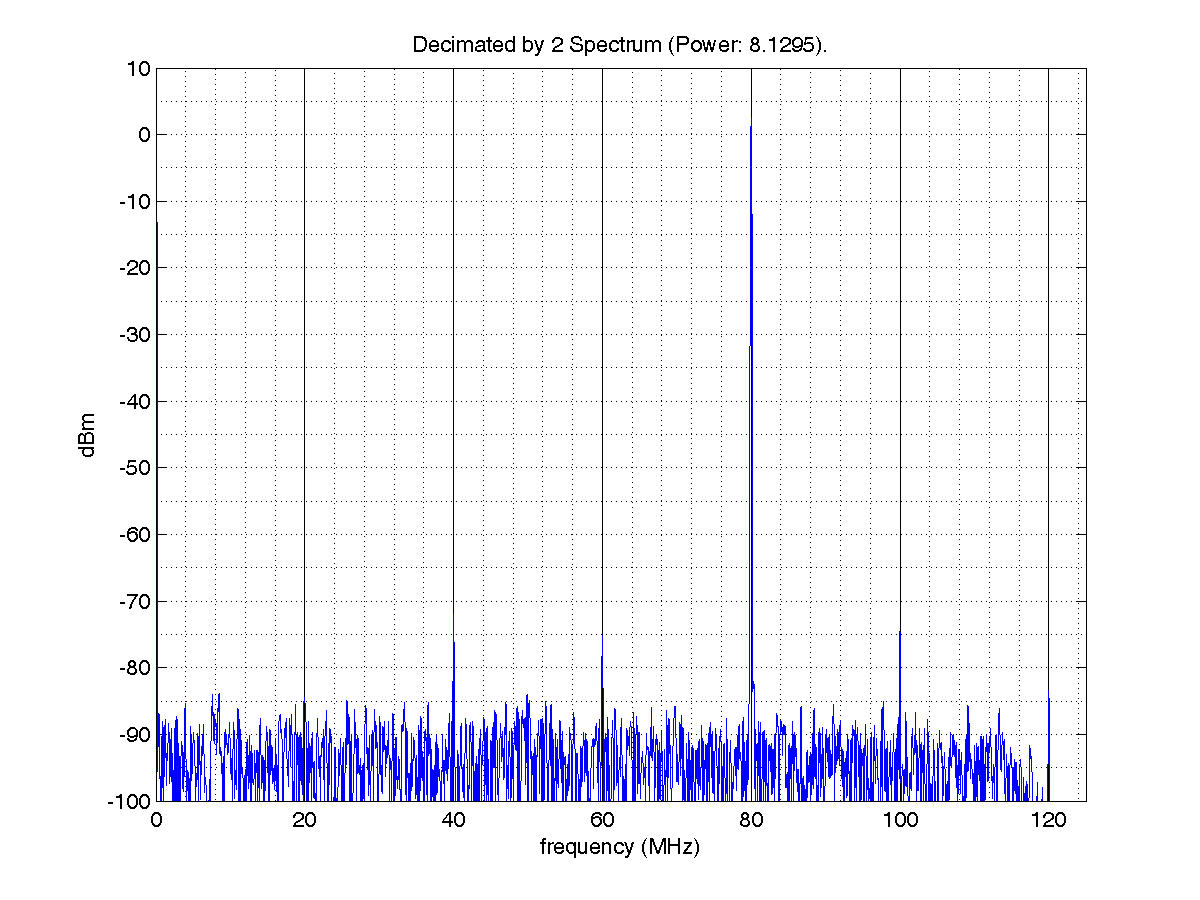

Sine Wave @ 80MHz; Decimated by 2; Frequency Domain

-

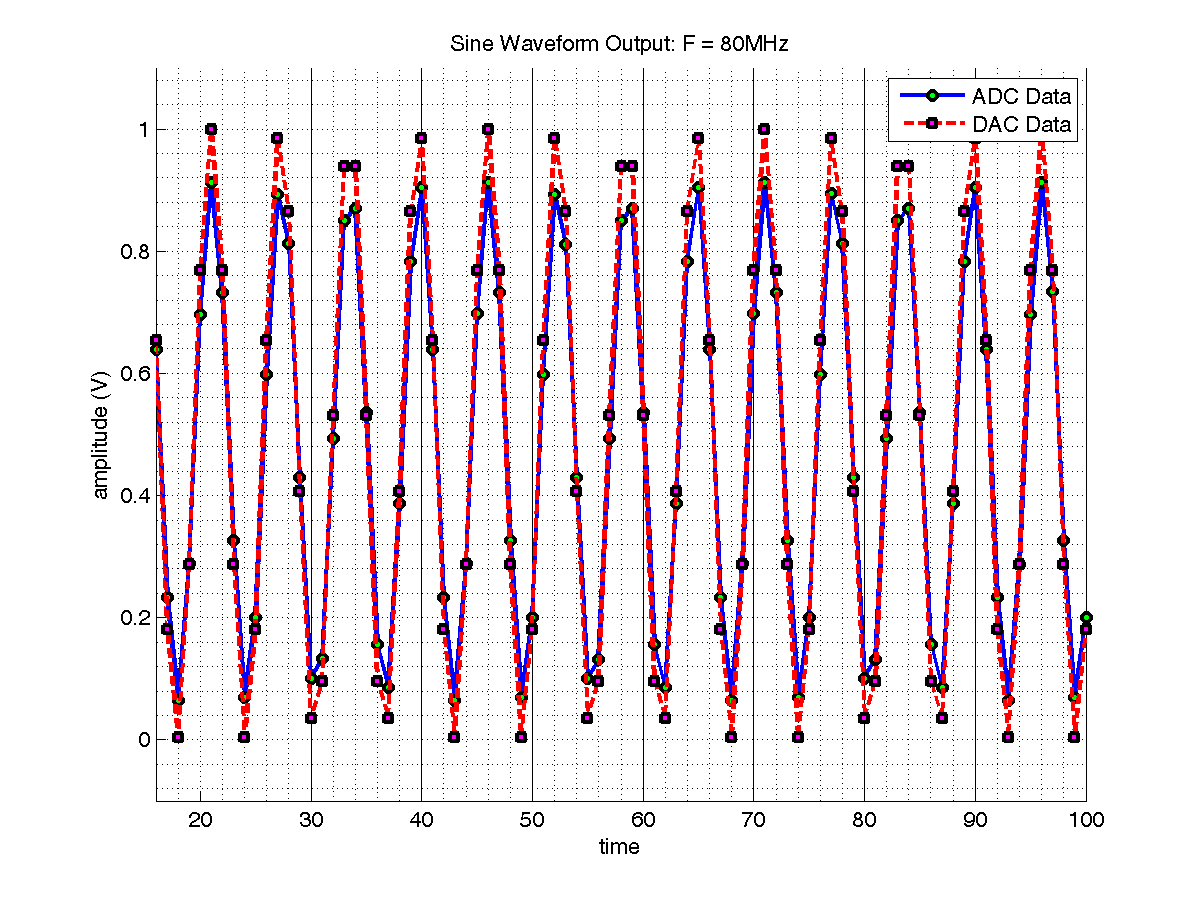

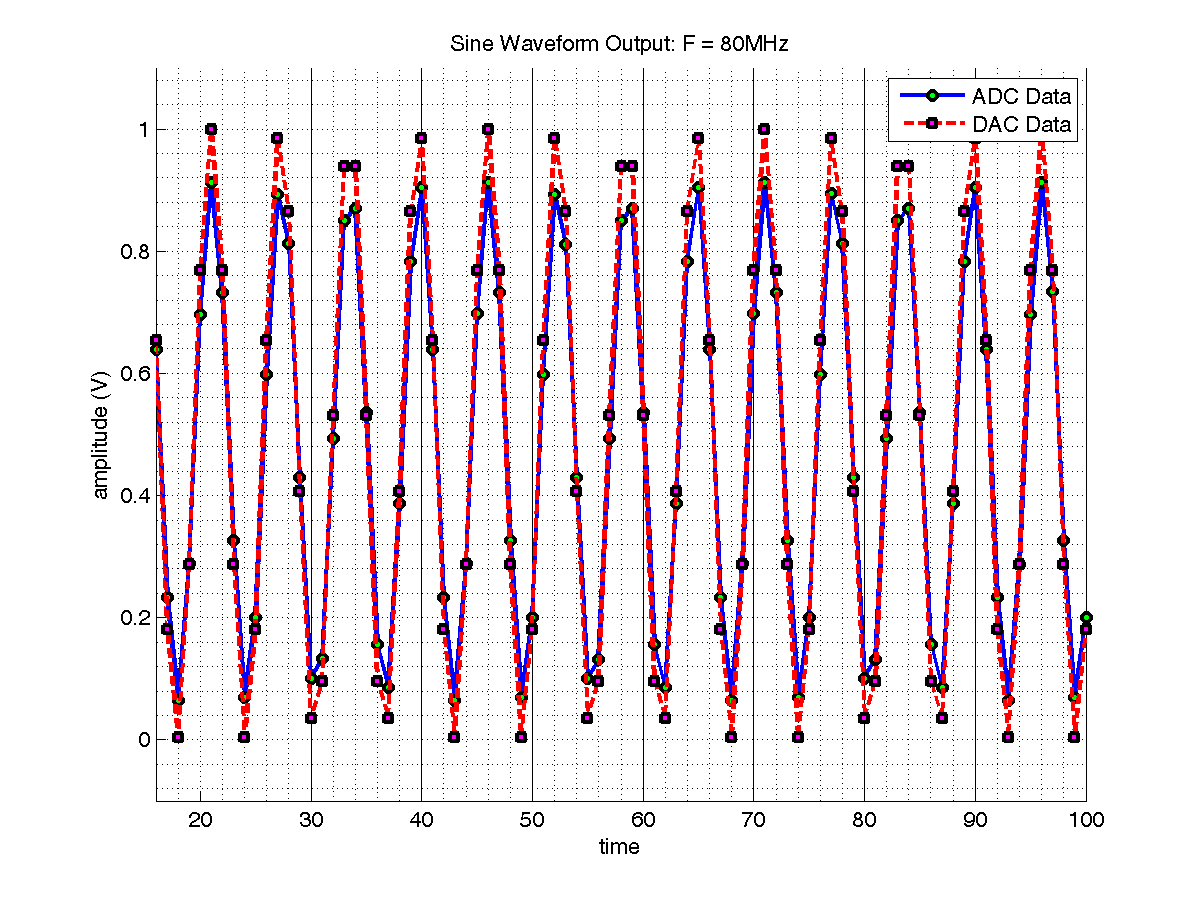

Sine Wave @ 80MHz; Time Domain; ADC Data on top of DAC Data

-

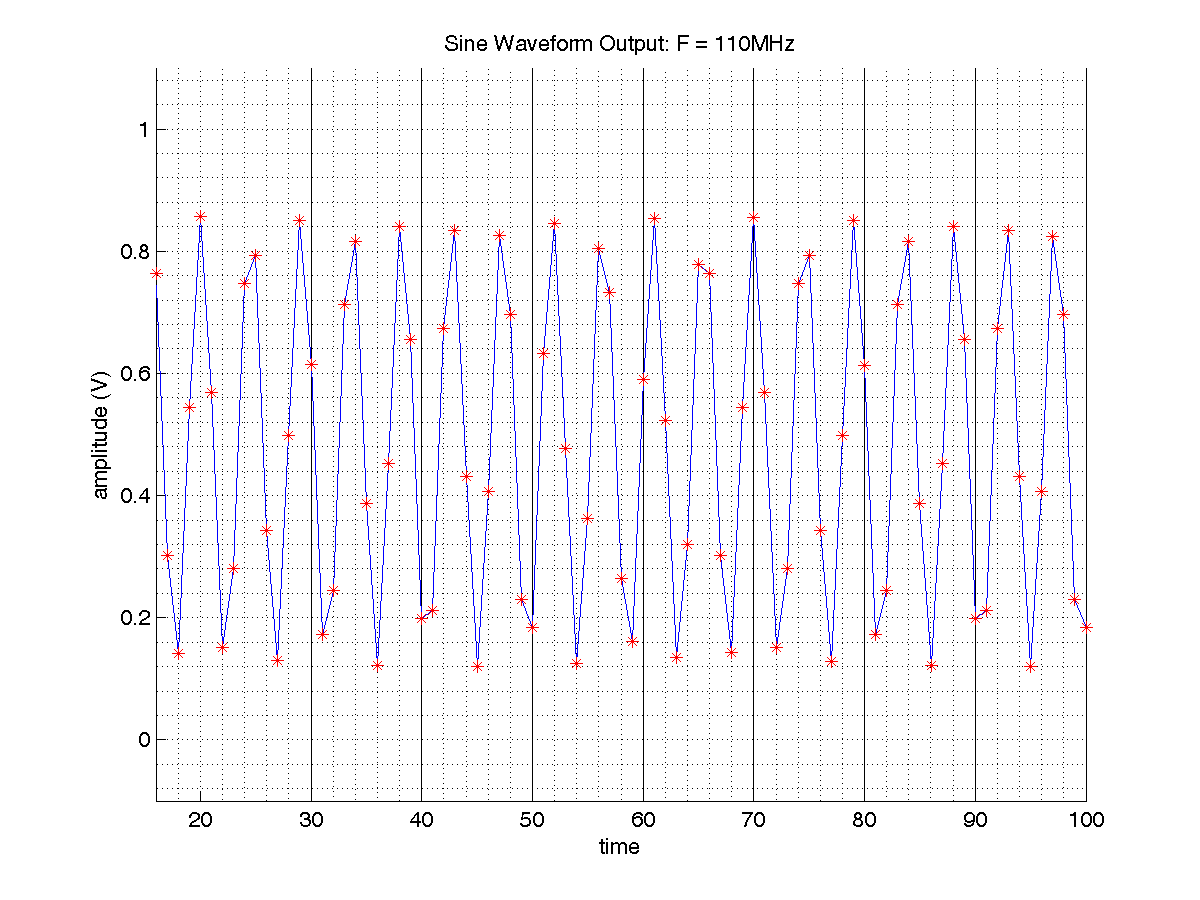

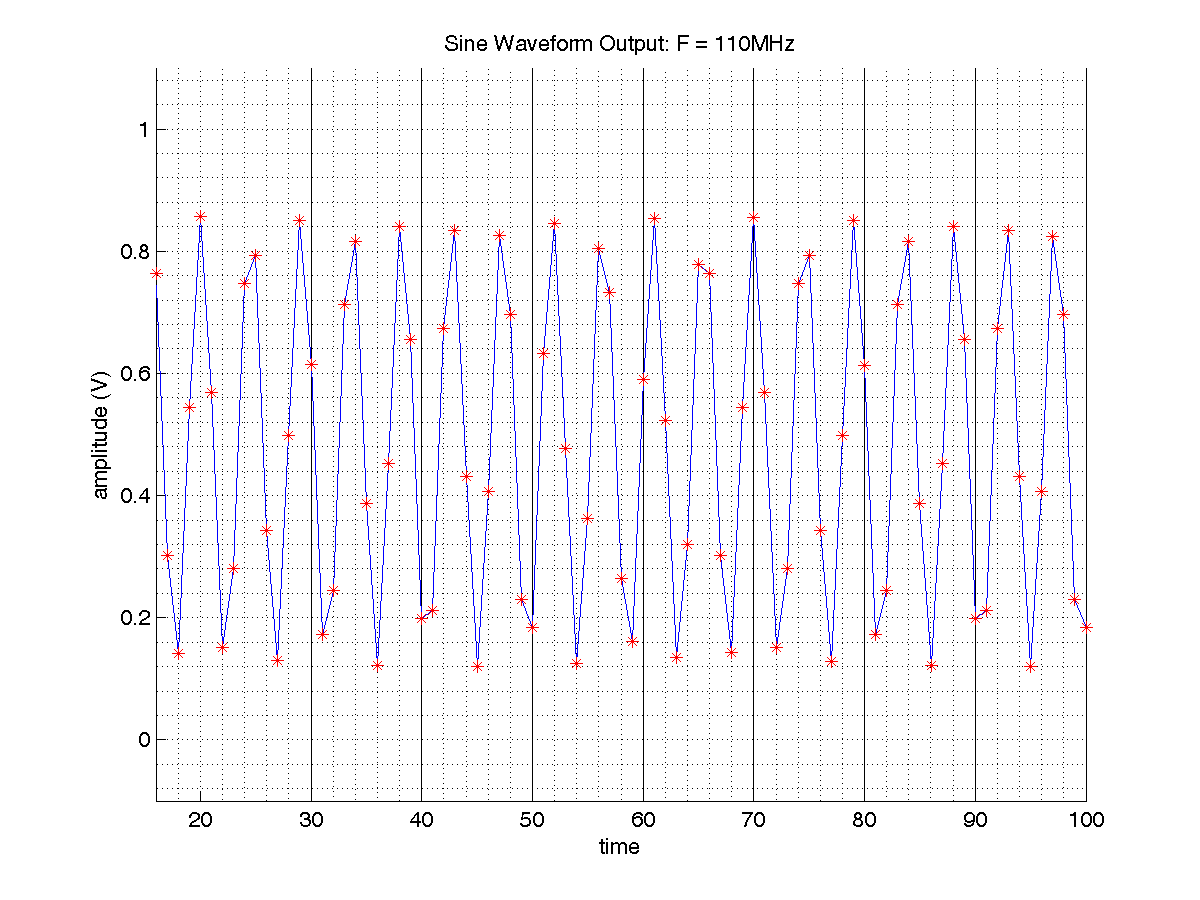

Sine Wave @ 110MHz; Time Domain

-

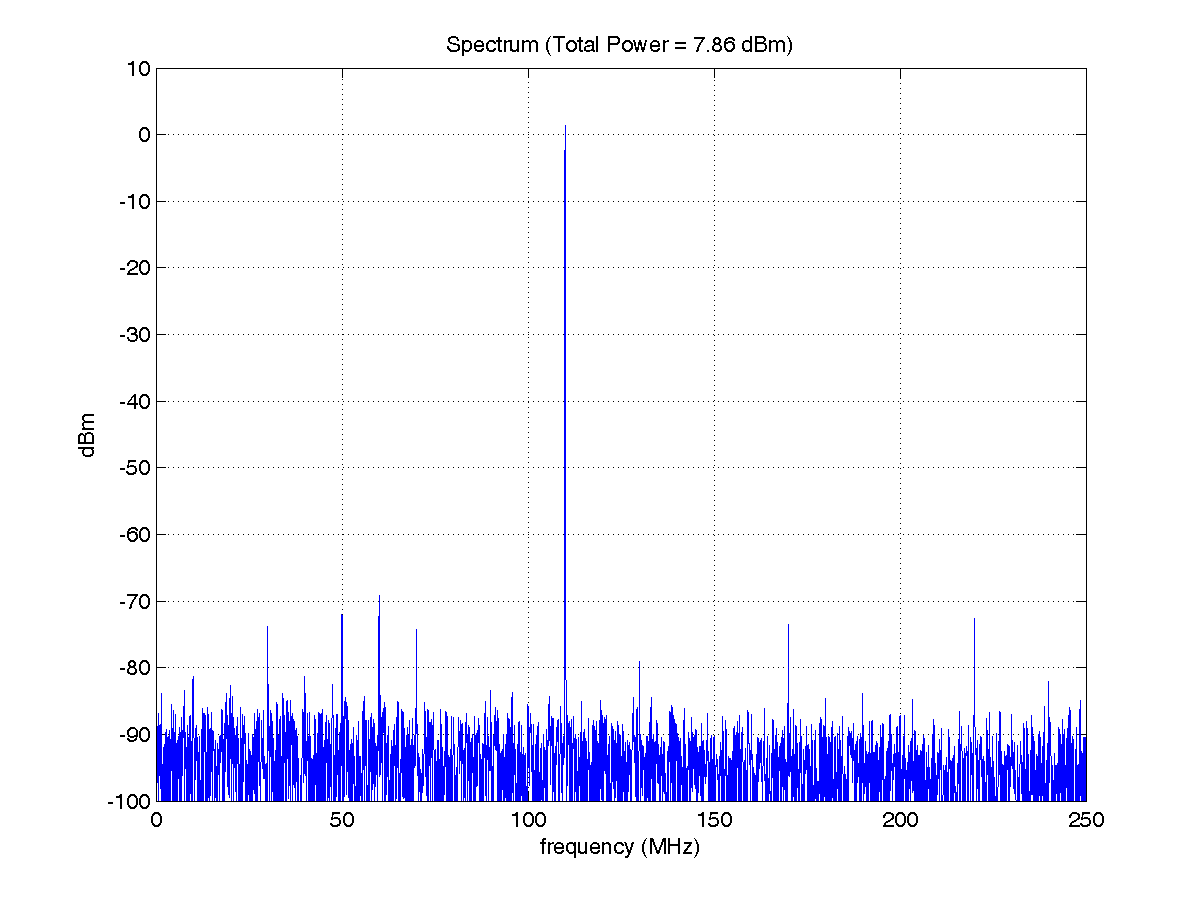

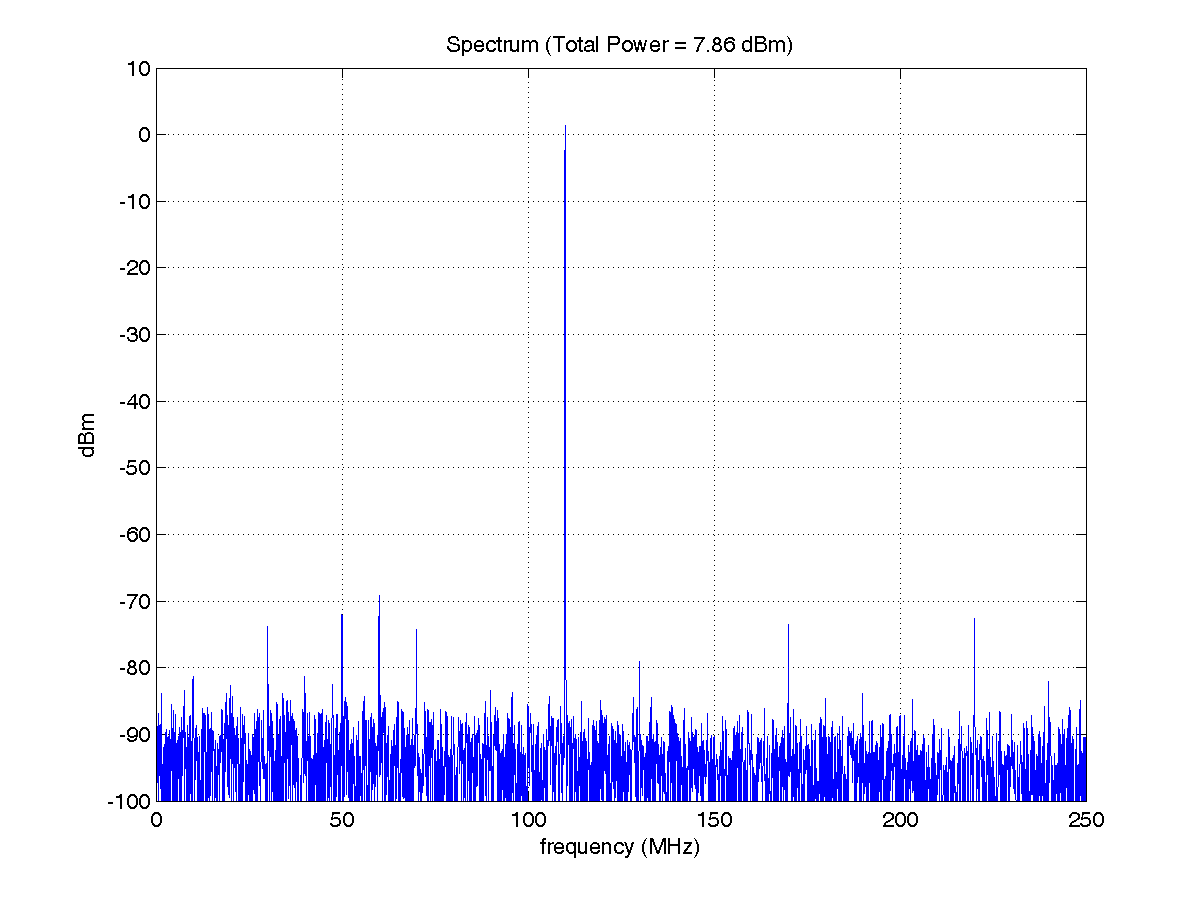

Sine Wave @ 110MHz; Frequency Domain

-

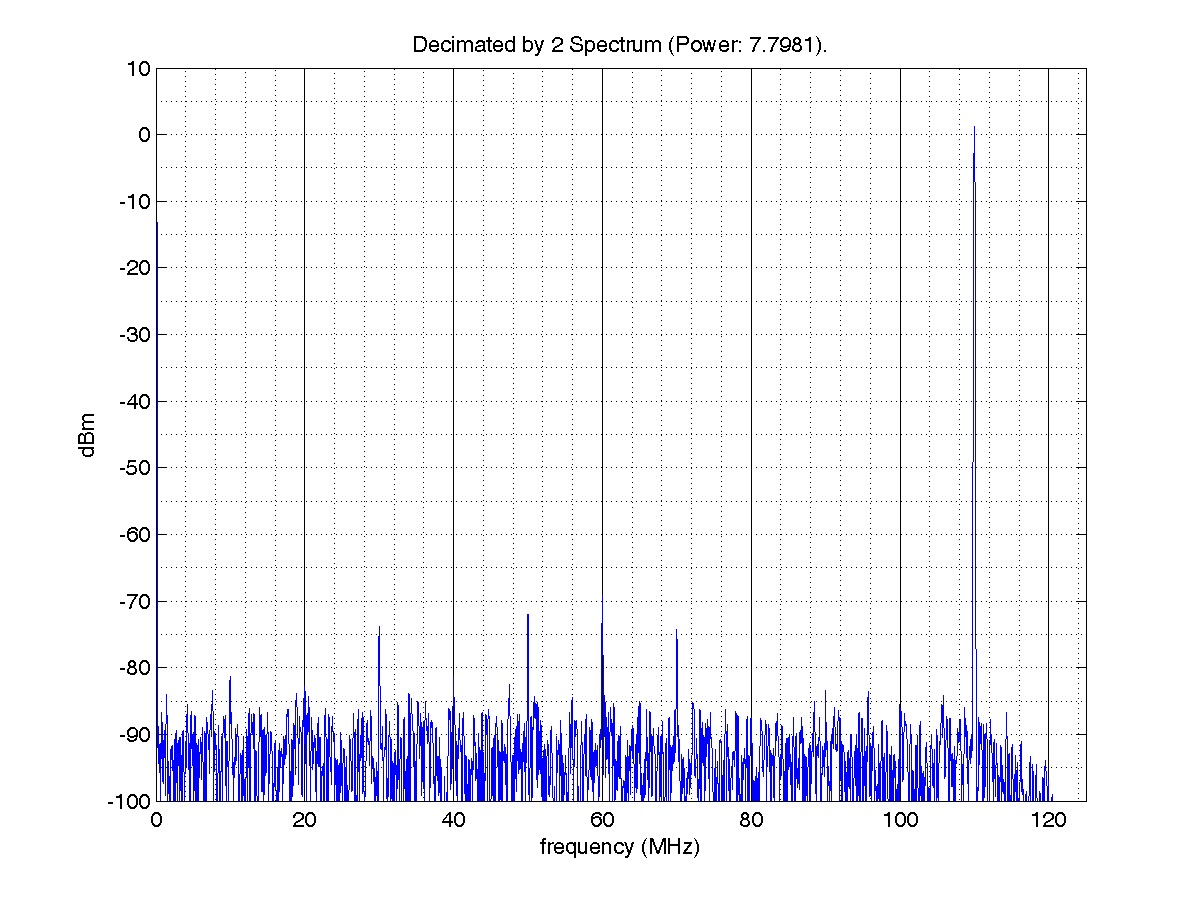

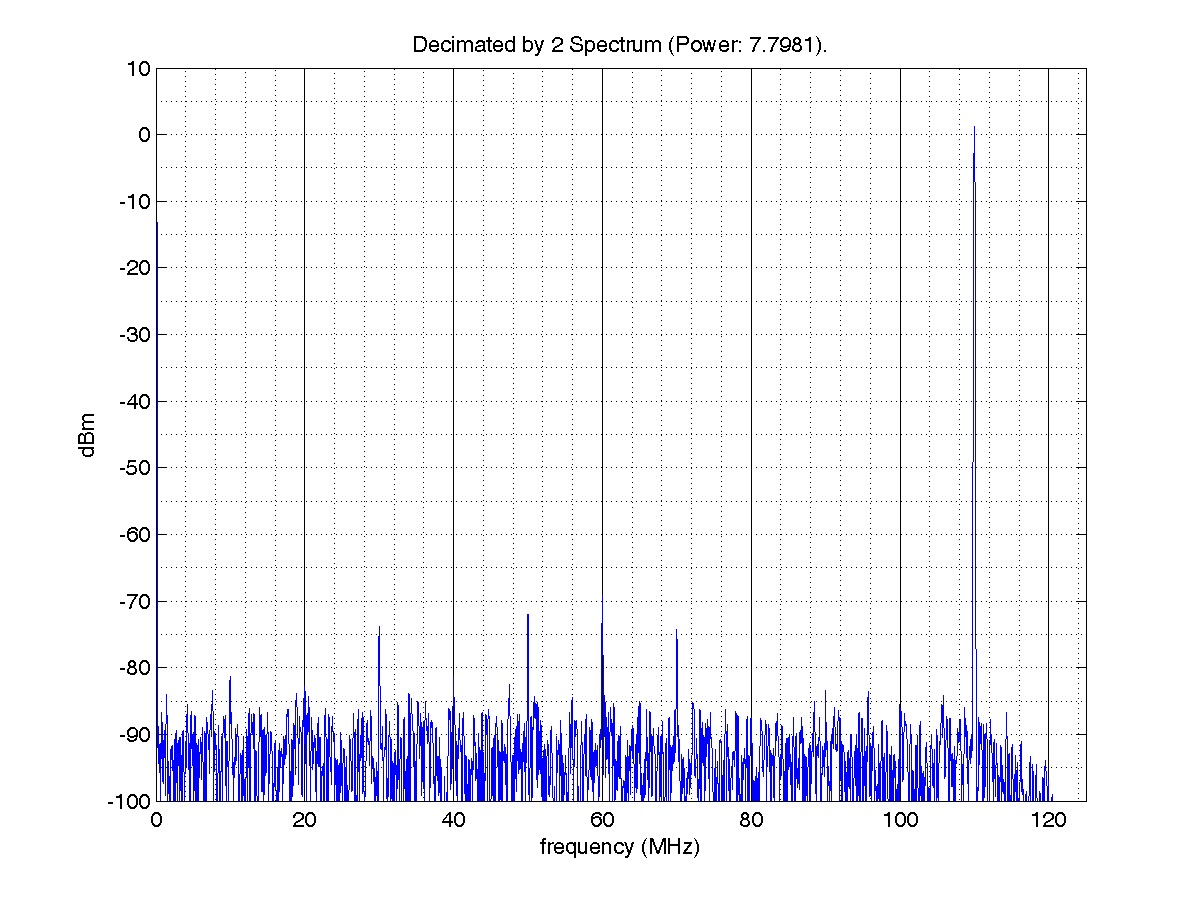

Sine Wave @ 110MHz; Decimated by 2; Frequency Domain

-

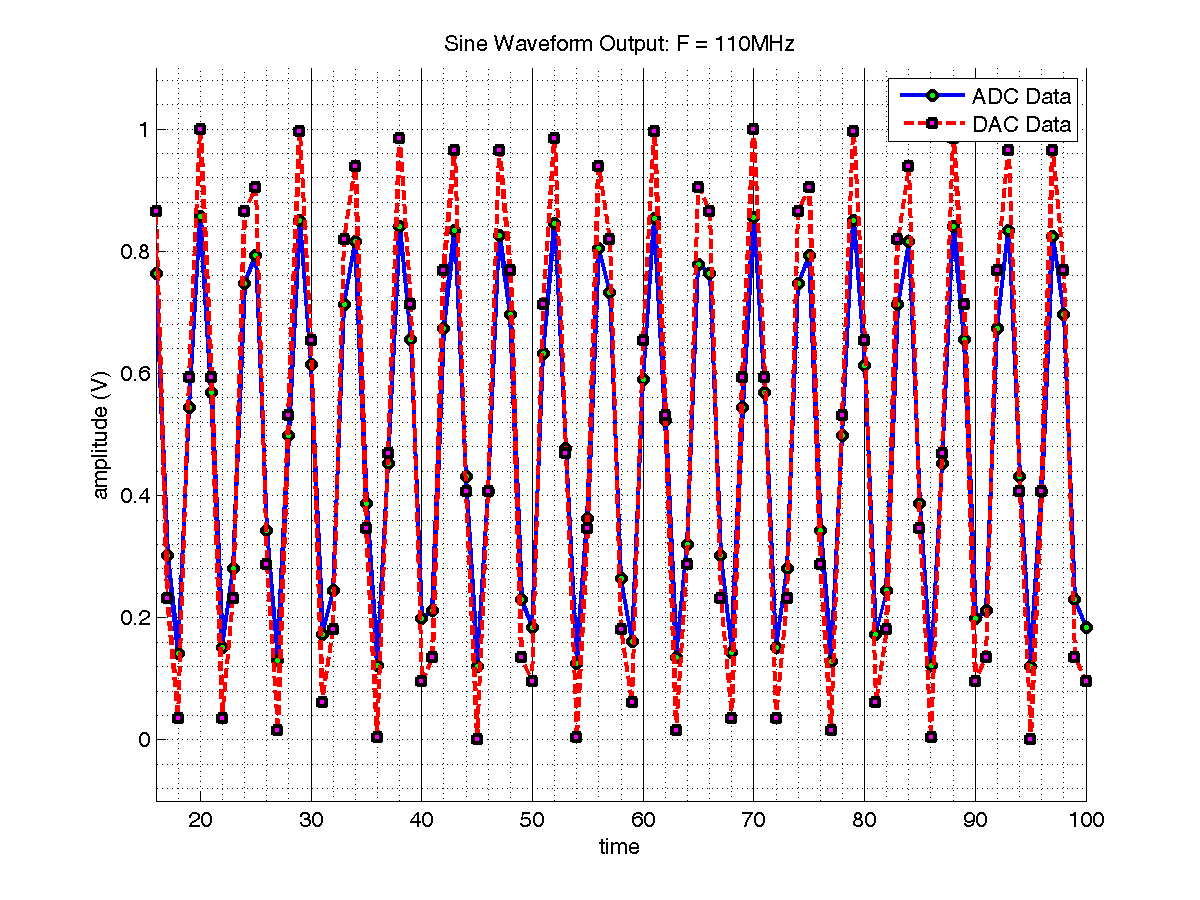

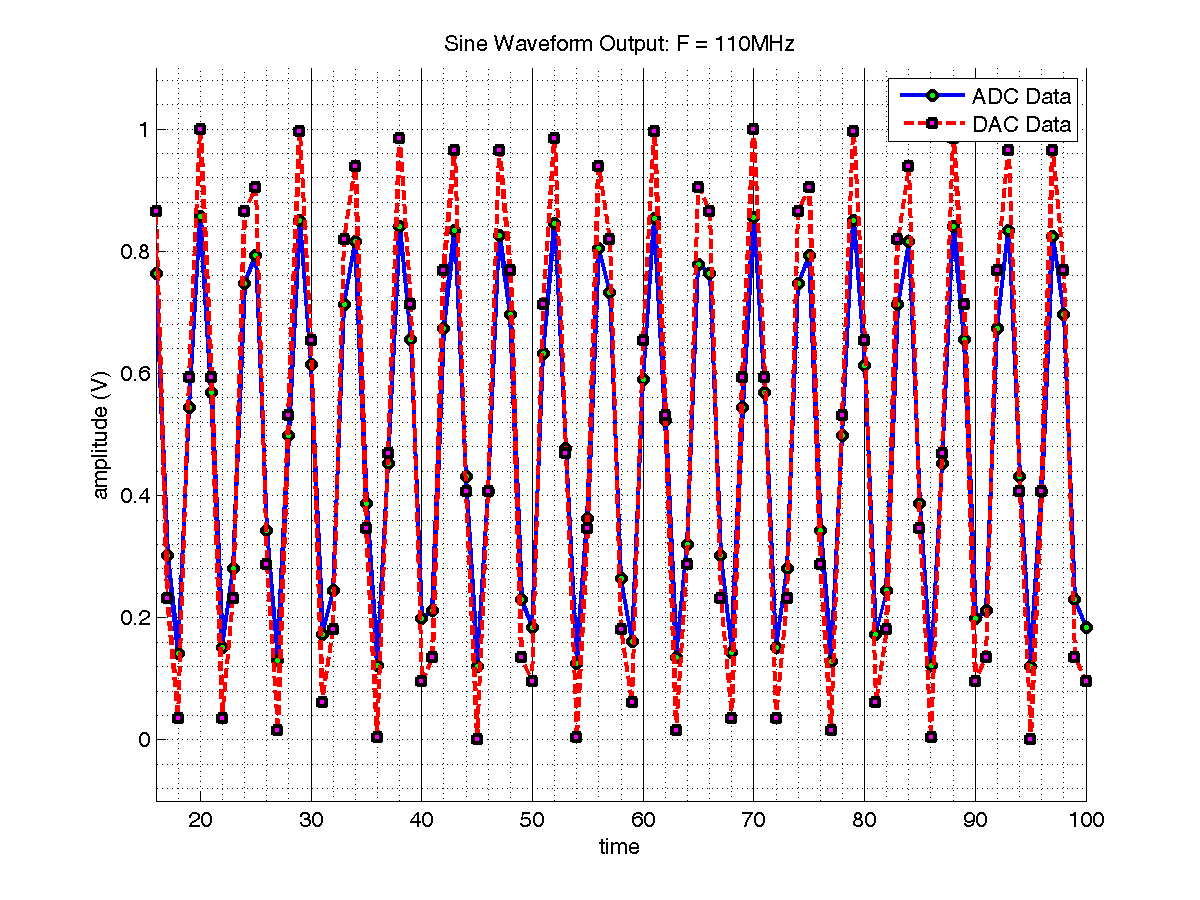

Sine Wave @ 110MHz; Time Domain; ADC Data on top of DAC Data

-

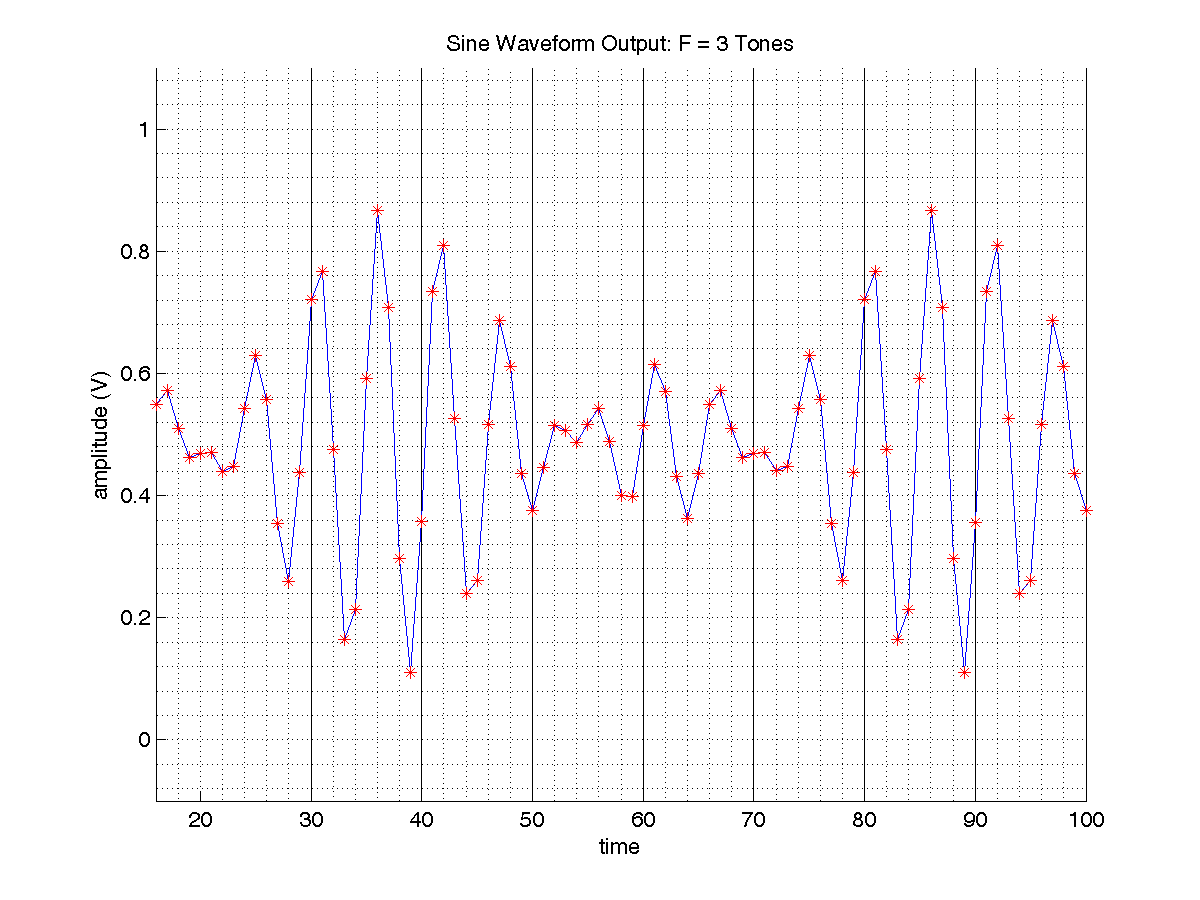

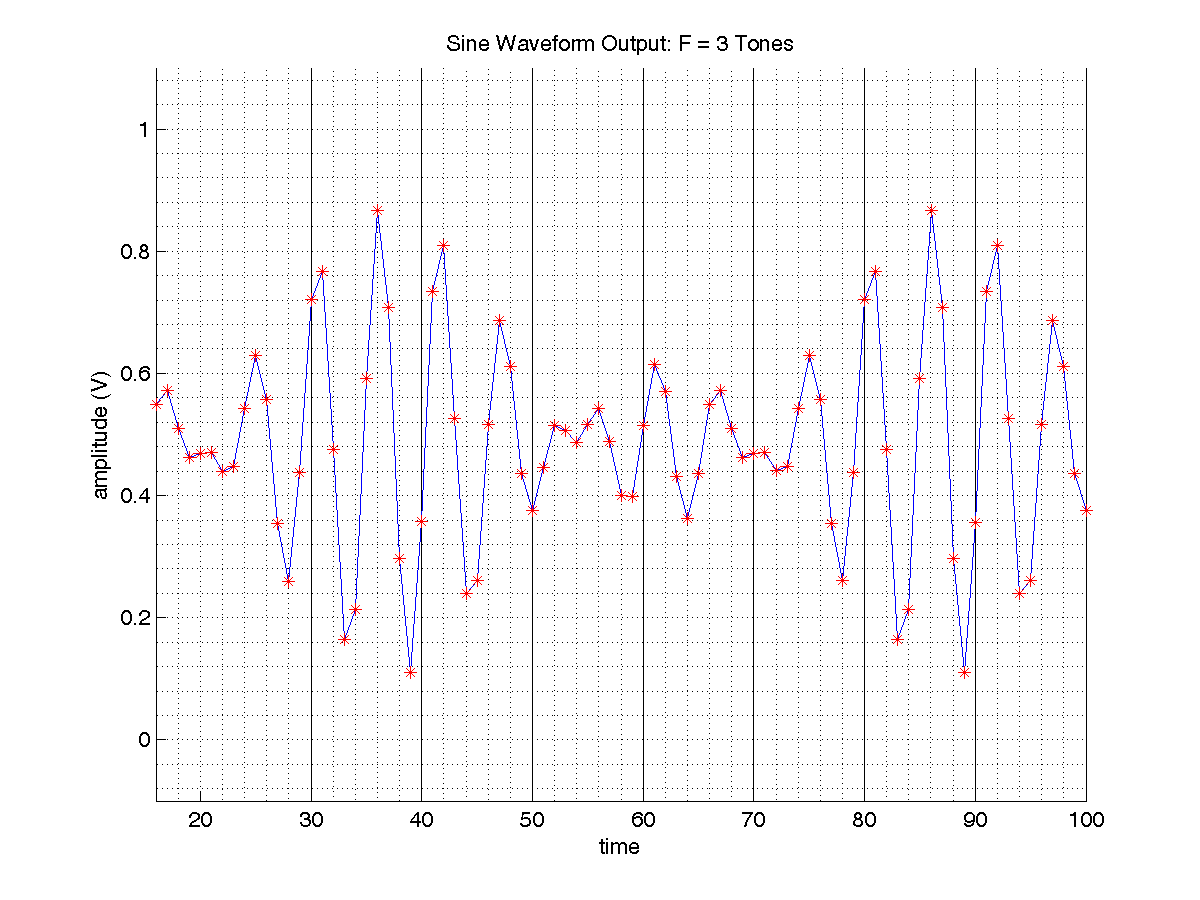

Sine Wave @ 80MHz, 90MHz, and 100MHz; Time Domain

-

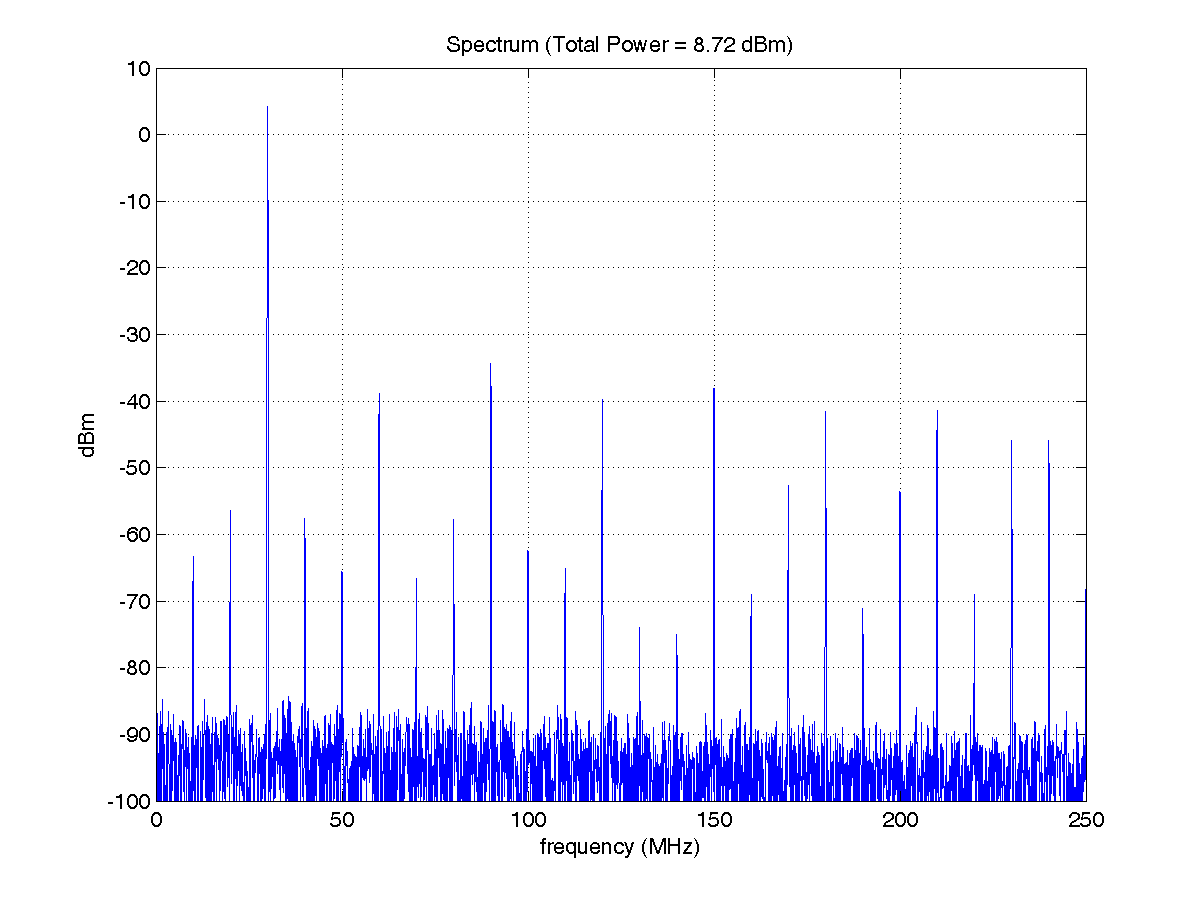

Sine Wave @ 80MHz, 90MHz, and 100MHz; Frequency Domain

-

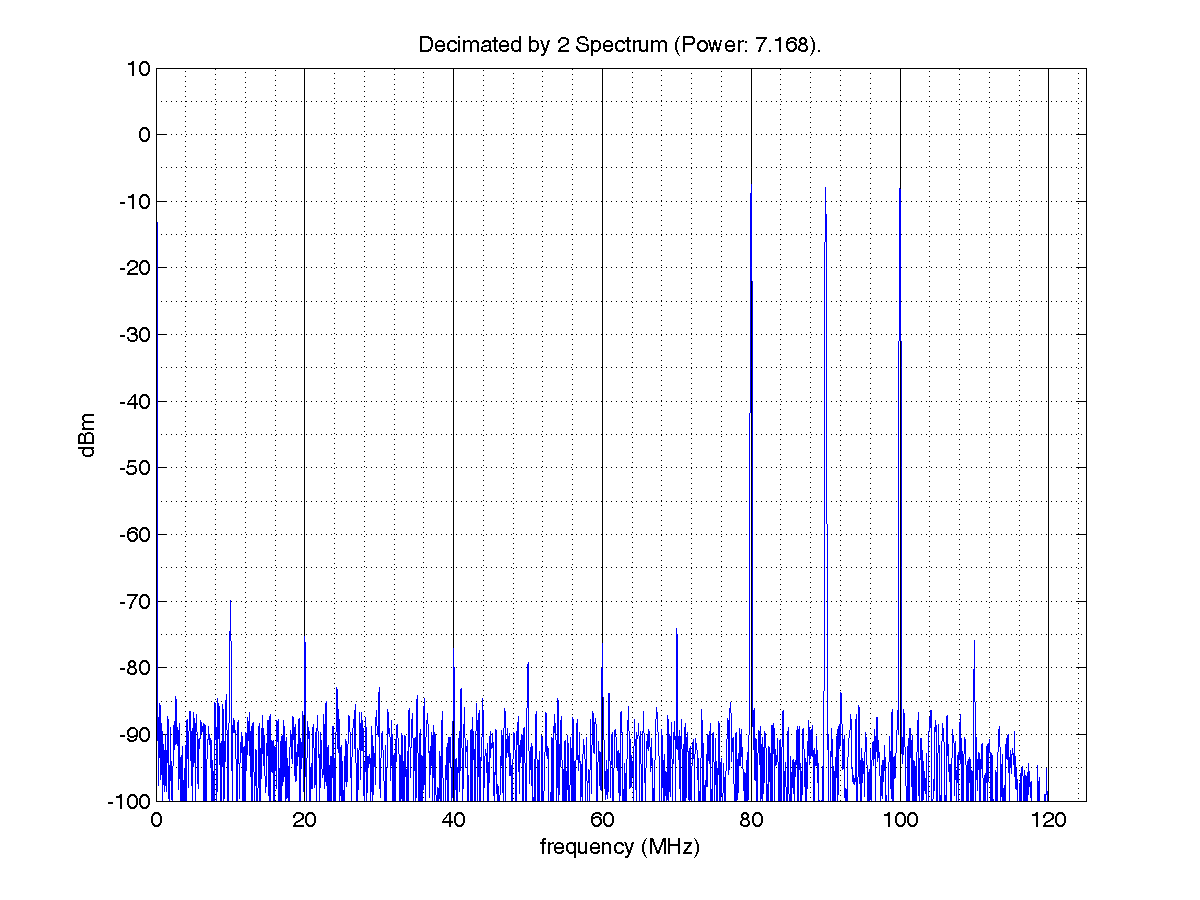

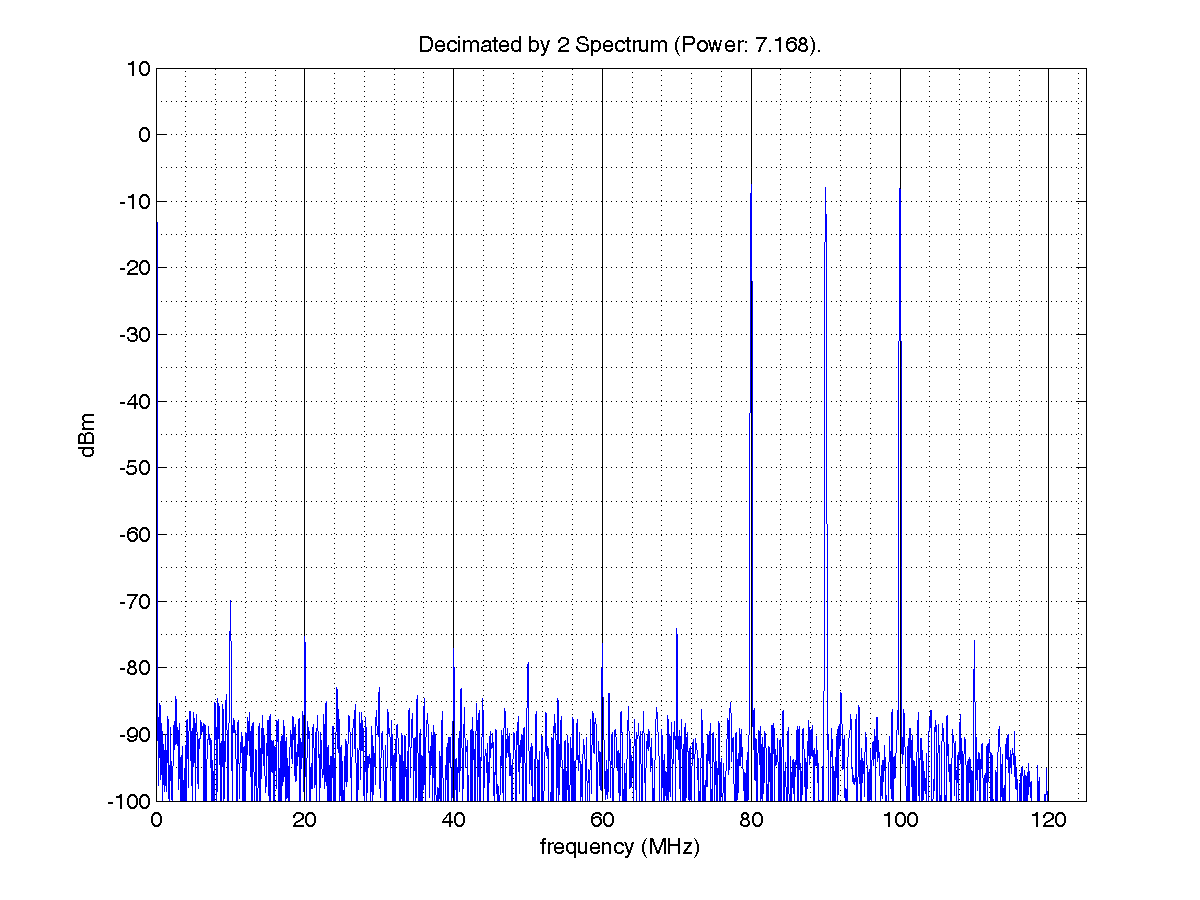

Sine Wave @ 80MHz, 90MHz, and 100MHz; Decimated by 2; Frequency Domain

-

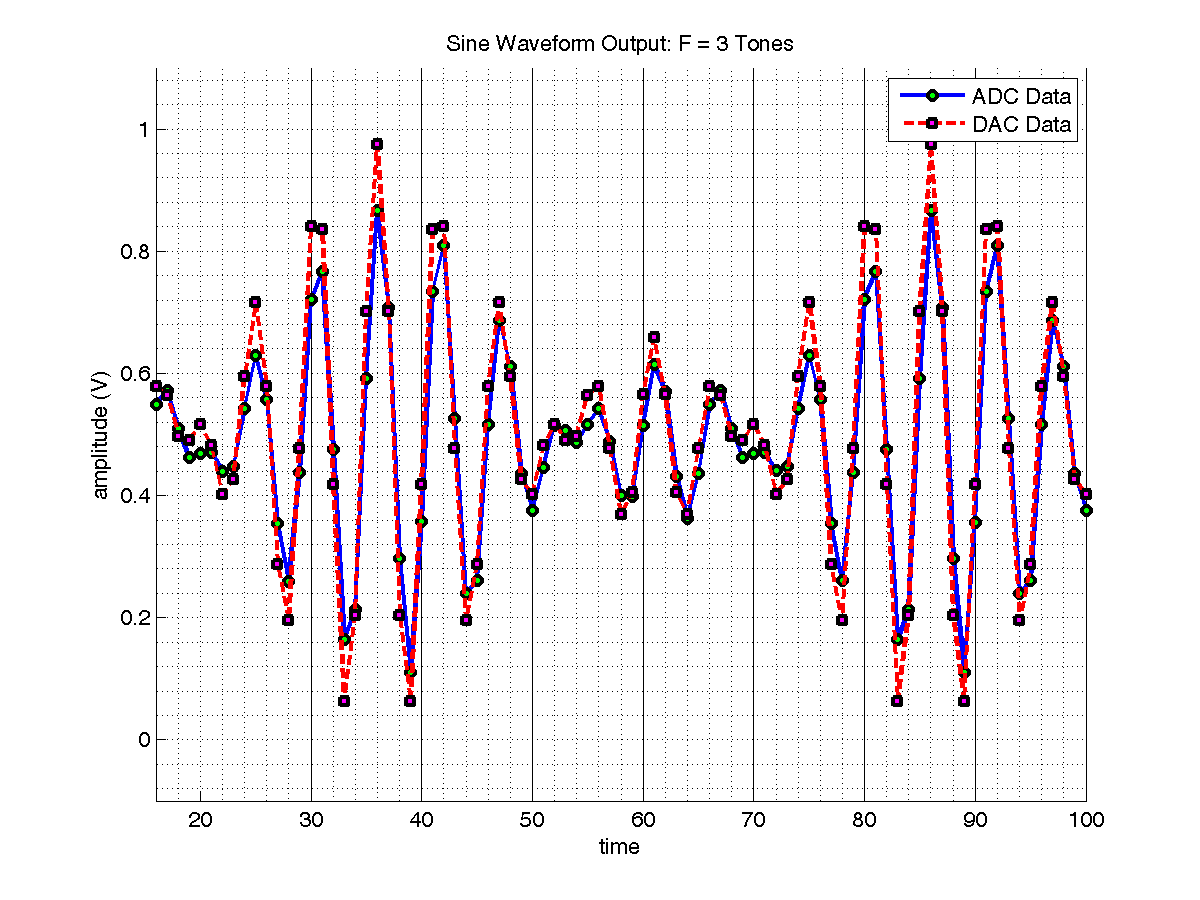

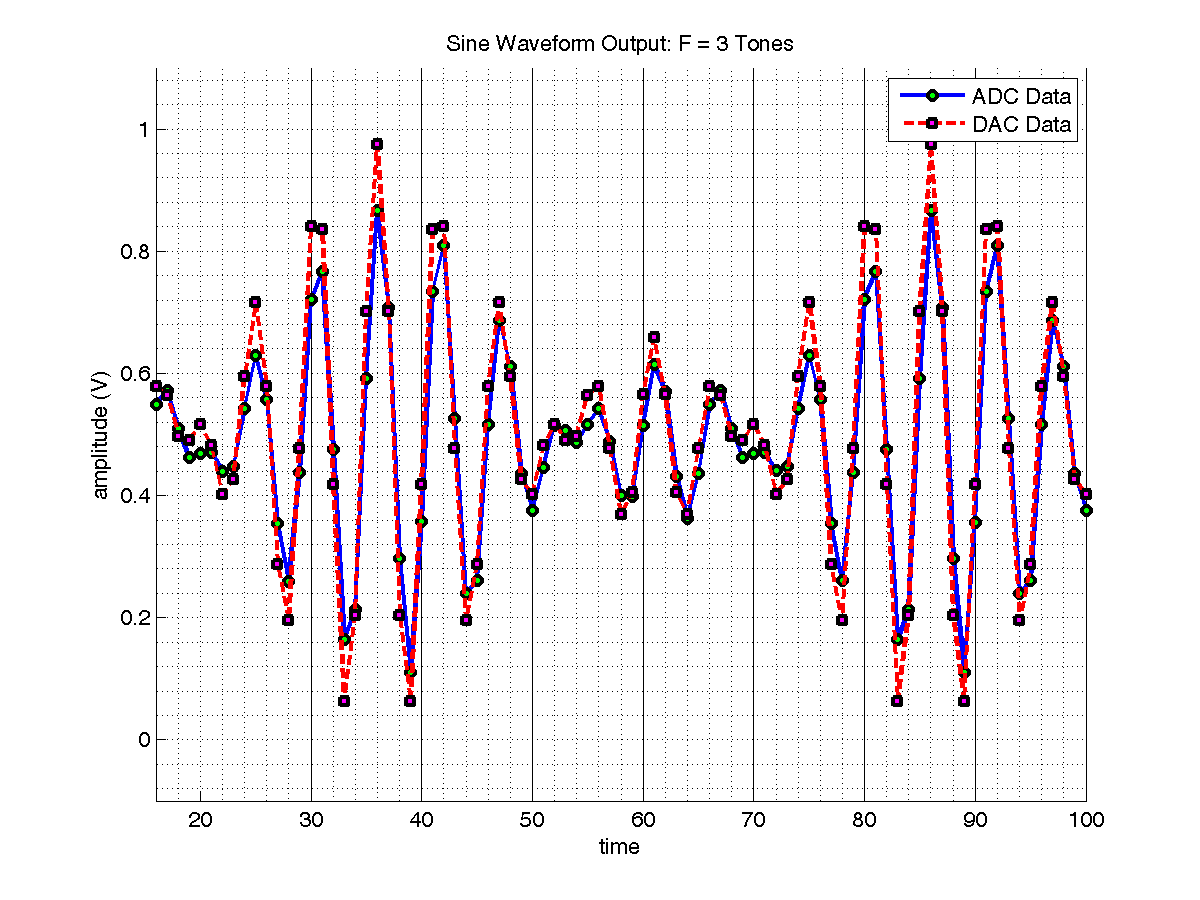

Sine Wave @ 80MHz, 90MHz, and 100MHz; Time Domain; ADC Data on top of DAC Data

Jeremy W. Webb

Graduate Student

Electrical and Computer Engineering Department

One Shields Avenue

Davis, CA 95616

Last Modified: Monday, March 27, 2017 10:19:56 PM

Last Modified: Monday, March 27, 2017 10:19:56 PM