# Xilinx<sup>®</sup> Virtex<sup>™</sup>-5 LX Evaluation Kit User Guide

# **Table of Contents**

| 1.0 In                                                                                                                                | troduction                                                                                                                                                                                                                                    |                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1.1                                                                                                                                   | Description                                                                                                                                                                                                                                   |                                                             |

| 1.2                                                                                                                                   | Board Features                                                                                                                                                                                                                                |                                                             |

| 1.3                                                                                                                                   | Test Files                                                                                                                                                                                                                                    |                                                             |

| 1.4<br>1.5                                                                                                                            | Reference Designs                                                                                                                                                                                                                             |                                                             |

| _                                                                                                                                     | Ordering Informationunctional Description                                                                                                                                                                                                     |                                                             |

| 2.0                                                                                                                                   | Xilinx Virtex-5 FPGA                                                                                                                                                                                                                          |                                                             |

| 2.2                                                                                                                                   | LVDS Interface                                                                                                                                                                                                                                |                                                             |

| 2.3                                                                                                                                   | Memory                                                                                                                                                                                                                                        |                                                             |

| 2.3.1                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.3.2                                                                                                                                 | Plash Memory                                                                                                                                                                                                                                  | .13                                                         |

| 2.4                                                                                                                                   | Clock Sources                                                                                                                                                                                                                                 |                                                             |

| 2.4.1                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.4.1                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.4.1                                                                                                                                 | 3                                                                                                                                                                                                                                             |                                                             |

| 2.4.1                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.5<br>2.5.1                                                                                                                          | Communication                                                                                                                                                                                                                                 |                                                             |

| 2.5.1                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.5.1                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.6                                                                                                                                   | User Switches                                                                                                                                                                                                                                 | _                                                           |

| 2.7                                                                                                                                   | User LEDs                                                                                                                                                                                                                                     |                                                             |

| 2.8                                                                                                                                   | Configuration Port                                                                                                                                                                                                                            |                                                             |

| 2.8.1                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.8.2                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.8.2                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.8.2                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.8.2                                                                                                                                 | ` /                                                                                                                                                                                                                                           |                                                             |

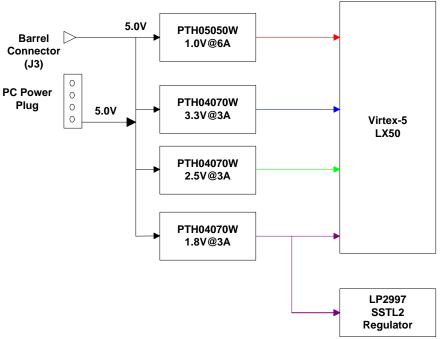

| 2.9<br>2.9.1                                                                                                                          | Power                                                                                                                                                                                                                                         |                                                             |

| 2.9.1                                                                                                                                 | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                       |                                                             |

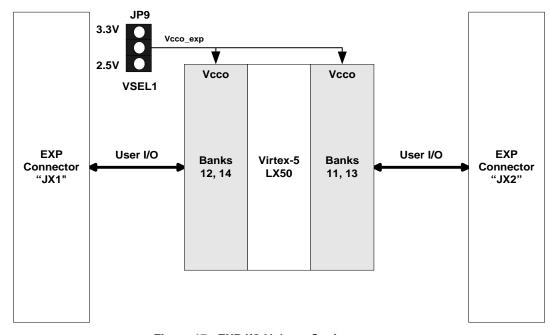

| 2.10                                                                                                                                  | Expansion Connectors                                                                                                                                                                                                                          |                                                             |

| 2.10.                                                                                                                                 |                                                                                                                                                                                                                                               |                                                             |

| 2.11                                                                                                                                  | LCD Display                                                                                                                                                                                                                                   |                                                             |

| 3.0 Te                                                                                                                                | est Designs                                                                                                                                                                                                                                   | . 35                                                        |

| 3.1                                                                                                                                   | Factory Test                                                                                                                                                                                                                                  |                                                             |

| 3.2                                                                                                                                   | Ethernet Test                                                                                                                                                                                                                                 |                                                             |

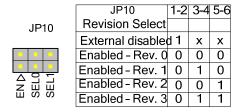

| 4.0 Re                                                                                                                                | evisions                                                                                                                                                                                                                                      | .37                                                         |

|                                                                                                                                       | Figures                                                                                                                                                                                                                                       |                                                             |

| Figure 1 - Vir                                                                                                                        | tex-5 LX Evaluation Board Picture                                                                                                                                                                                                             | 5                                                           |

|                                                                                                                                       | tex-5 LX Evaluation Board Block Diagram                                                                                                                                                                                                       | 7                                                           |

| Figure 3 - LV                                                                                                                         | DS connector – 80 pin                                                                                                                                                                                                                         | 8                                                           |

| •                                                                                                                                     | tex-5 LX Evaluation Board Memory Interfaces                                                                                                                                                                                                   |                                                             |

|                                                                                                                                       | DR2 SDRAM Interface                                                                                                                                                                                                                           |                                                             |

| •                                                                                                                                     | ock Nets Connected to Global Clock Inputs                                                                                                                                                                                                     |                                                             |

|                                                                                                                                       | S8442 Clock SynthesizerS8442 Clock Synthesizer Interface to the FPGA                                                                                                                                                                          |                                                             |

|                                                                                                                                       |                                                                                                                                                                                                                                               | . 1/                                                        |

|                                                                                                                                       | and NIDIP Switches for the LVDS Synthesizer                                                                                                                                                                                                   | 12                                                          |

|                                                                                                                                       | and N DIP Switches for the LVDS Synthesizer                                                                                                                                                                                                   |                                                             |

| Flaure 11 - R                                                                                                                         | 0/100/1000 Mb/s Ethernet Interface                                                                                                                                                                                                            | . 20                                                        |

|                                                                                                                                       |                                                                                                                                                                                                                                               | .20<br>.24                                                  |

| Figure 12 - J                                                                                                                         | 0/100/1000 Mb/s Ethernet Interface                                                                                                                                                                                                            | .20<br>.24<br>.26                                           |

| Figure 12 - J<br>Figure 13 - Ju<br>Figure 14 - S                                                                                      | 0/100/1000 Mb/s Ethernet Interface                                                                                                                                                                                                            | .20<br>.24<br>.26<br>.27                                    |

| Figure 12 - J<br>Figure 13 - Ju<br>Figure 14 - S<br>Figure 15 - P                                                                     | 0/100/1000 Mb/s Ethernet Interface                                                                                                                                                                                                            | .20<br>.24<br>.26<br>.27<br>.28                             |

| Figure 12 - J <sup>-</sup><br>Figure 13 - Ju<br>Figure 14 - S<br>Figure 15 - P<br>Figure 16 - M                                       | 0/100/1000 Mb/s Ethernet Interface                                                                                                                                                                                                            | .20<br>.24<br>.26<br>.27<br>.28<br>.29                      |

| Figure 12 - J<br>Figure 13 - Ju<br>Figure 14 - S<br>Figure 15 - P<br>Figure 16 - M<br>Figure 17 - E                                   | 0/100/1000 Mb/s Ethernet Interface  S232 Interface  TAG Chain on the Virtex-5 LX Evaluation Board  umper Settings for Master SelectMAP mode  AM Interface (50-pin header)  C4 JTAG Port Connector  fain Power Supply  XP I/O Voltage Settings | .20<br>.24<br>.26<br>.27<br>.28<br>.29<br>.30               |

| Figure 12 - J<br>Figure 13 - Ju<br>Figure 14 - S<br>Figure 15 - P<br>Figure 16 - M<br>Figure 17 - E<br>Figure 18 - B                  | 0/100/1000 Mb/s Ethernet Interface                                                                                                                                                                                                            | .20<br>.24<br>.26<br>.27<br>.28<br>.29<br>.30<br>.31        |

| Figure 12 - J<br>Figure 13 - Ju<br>Figure 14 - S<br>Figure 15 - P<br>Figure 16 - M<br>Figure 17 - E<br>Figure 18 - B<br>Figure 19 - P | 0/100/1000 Mb/s Ethernet Interface  S232 Interface  TAG Chain on the Virtex-5 LX Evaluation Board  umper Settings for Master SelectMAP mode  AM Interface (50-pin header)  C4 JTAG Port Connector  fain Power Supply  XP I/O Voltage Settings | .20<br>.24<br>.26<br>.27<br>.28<br>.29<br>.30<br>.31<br>.38 |

# **Tables**

| Table 1 - Ordering Information                          |    |

|---------------------------------------------------------|----|

| Table 2 - 5VLX50 Features                               | 8  |

| Table 3 - Virtex-5 LVDS Pin Assignments                 |    |

| Table 4 - DDR2 SDRAM Timing Parameters                  | 11 |

| Table 5 - Virtex-5 DDR2 FPGA Pinouts                    | 12 |

| Table 6 - Virtex-5 Flash Memory Pinout                  |    |

| Table 7 - On-Board Clock Sources                        |    |

| Table 8 - Clock Socket "U5" Pin-out                     | 14 |

| Table 9 - User Clock Input                              | 14 |

| Table 10 - ICS8442 Clock Synthesizer Pin Description    |    |

| Table 11 - ICS8442 N Settings                           | 16 |

| Table 12 - Example of the ICS8442 M and N Settings      |    |

| Table 13 - DIP Switch Setting for M[8:0]                |    |

| Table 14 - DIP Switch Setting for N[1:0]                |    |

| Table 15 - Synthesizer Clock Outputs for M and N Values |    |

| Table 16 - ICS8442 Pin Assignments                      |    |

| Table 17 - Ethernet PHY Hardware Strapping Options      |    |

| Table 18 - Ethernet PHY Pin Assignments                 |    |

| Table 19 - USB Interface FPGA Pin-out                   |    |

| Table 20 - RS232 Signals                                |    |

| Table 21 - RS232 Port Jumper Settings                   |    |

| Table 22 - Push Button Pin Assignments                  |    |

| Table 23 - DIP Switch Pin Assignments                   |    |

| Table 24 - LED Pin Assignments                          | 25 |

| Table 25 - FPGA Configuration Modes                     |    |

| Table 26 - JTAG Jumper Configurations                   |    |

| Table 27 - SAM Interface Signals                        |    |

| Table 28 - I/O Bank Voltages                            |    |

| Table 29 - EXP Connector Signals                        |    |

| Table 30 - EXP Connector "JX1" Pin-out                  |    |

| Table 31 - EXP Connector "JX2" Pin-out                  |    |

| Table 32 - Test Designs (in Configuration PROM)         | 35 |

# 1.0 Introduction

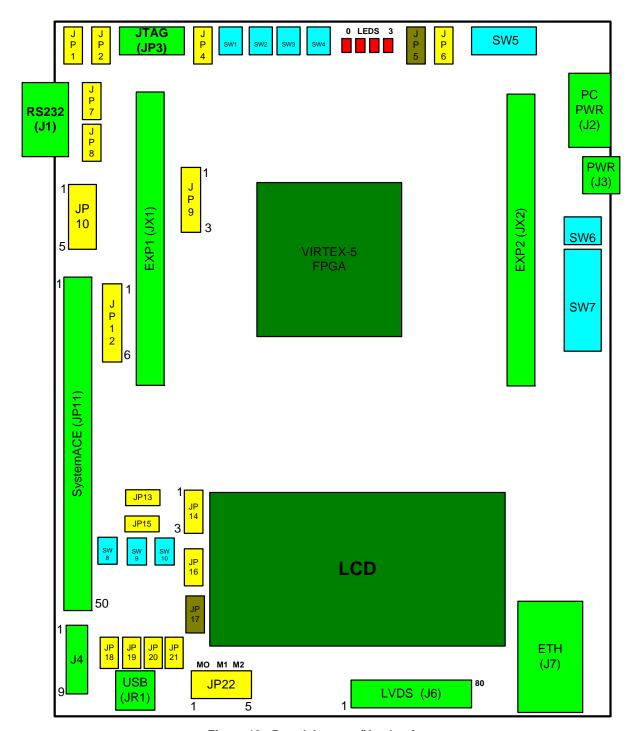

The purpose of this manual is to describe the functionality and contents of the Virtex-5 LX Evaluation Kit from Avnet Electronics Marketing. This document includes instructions for operating the board, descriptions of the hardware features and explanations of the test code programmed in the on-board PROM. For reference design documentation, see the PDF file included with the project files of the design.

# 1.1 Description

The Virtex-5 LX Evaluation Kit provides a complete hardware environment for designers to accelerate their time to market. The kit delivers a stable platform to develop and test designs targeted to the advanced Xilinx FPGA family. The installed Virtex-5 LX device offers a prototyping environment to effectively demonstrate the enhanced benefits of leading edge Xilinx FPGA solutions. Reference designs are included with the kit to exercise standard peripherals on the Evaluation board for a quick start to device familiarization.

#### 1.2 Board Features

# **FPGA**

- Xilinx Virtex-5

- o XC5VLX50-FF676 FPGA

- XC5VLX110-FF676 FPGA

#### I/O Connectors

- Two EXP™ general-purpose I/O expansion connectors

- One 0.1" USB Debug Header

- One 50-pin 0.1" Header supports Avnet System ACE Module (SAM)

- 80 pin LVDS connector supports 10-bit plus Frame and Clock TX and RX data.

#### Memory

- 64 MB DDR2 SDRAM

- 16 MB FLASH

# Communication

- RS-232 serial port

- USB 2.0

- 10/100/1000 Ethernet

## **Power**

- Regulated 3.3V, 2.5V, 1.8V, and 0.9V supply voltages derived from an external 5V supply

- SSTL2 Termination Regulator

## Configuration

- XCF32P 32Mbit configuration PROM

- Xilinx Parallel Cable IV or Platform USB Cable support for JTAG Programming/Configuration

#### **Display**

2x16 character LCD display

## 1.3 Test Files

The configuration PROM on the Virtex-5 LX Evaluation Board comes programmed with test designs that can be used as base tests for the peripherals on the board. The test designs listed below are discussed in Section 3.0.

- USB/LCD Test

- Factory Test

- Ethernet Test

## 1.4 Reference Designs

Reference designs that demonstrate some of the potential applications of the Virtex-5 LX Evaluation board can be downloaded from the Avnet Design Resource Center (<a href="www.em.avnet.com/drc">www.em.avnet.com/drc</a>). The reference designs include all of the source code and project files necessary to implement the designs. See the PDF document included with each reference design for a complete description of the design and detailed instructions for running a demonstration on the Evaluation board. Check the DRC periodically for updates and new designs.

- V5LX Evaluation Boot Loader Example Design

- V5LX Evaluation Interrupt Example Design

- V5LX Evaluation Xilinx Micro Kernel (XMK) Example Design

- V5LX Evaluation IwIP Web Server Example Design

- V5LX Evaluation System ACE Module Example Design

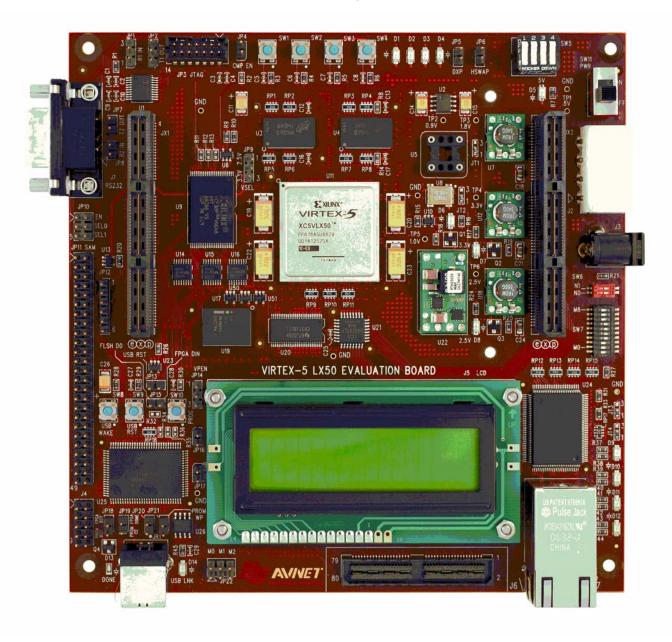

Figure 1 - Virtex-5 LX Evaluation Board Picture

# 1.5 Ordering Information

The following table lists the Evaluation kit part numbers and available software options. Internet link at <a href="http://www.em.avnet.com/drc">http://www.em.avnet.com/drc</a>

| Part Number           | Hardware                                                                            |

|-----------------------|-------------------------------------------------------------------------------------|

| AES-XLX-V5LX-EVL50-G  | Xilinx Virtex-5 LX Evaluation Kit populated with an XC5VLX50 -1 speed grade device  |

| AES-XLX-V5LX-EVL110-G | Xilinx Virtex-5 LX Evaluation Kit populated with an XC5VLX110 -1 speed grade device |

**Table 1 - Ordering Information**

# 2.0 Functional Description

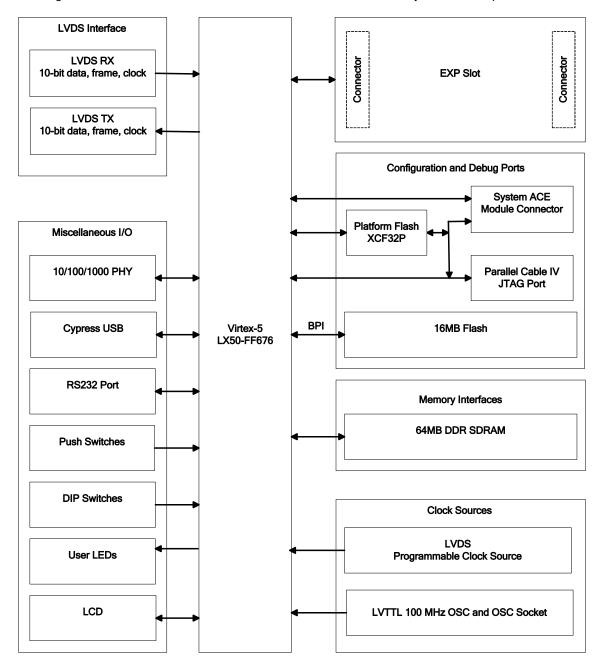

A high-level block diagram of the Virtex-5 LX Evaluation board is shown below followed by a brief description of each sub-section.

Figure 2 - Virtex-5 LX Evaluation Board Block Diagram

## 2.1 Xilinx Virtex-5 FPGA

The Virtex-5 LX50 FPGA feature 12 DCMs, 6 PLLs, and 1.25Gbps LVDS I/O. The following table shows some other main features of the FF676 package.

| Device   | Number of Slices | BlockRAM<br>(Kb) | Xtreme DSP<br>Slices | DSP48E<br>Slices |

|----------|------------------|------------------|----------------------|------------------|

| XC5VLX50 | 7,200            | 1,728            | 128                  | 48               |

Table 2 - 5VLX50 Features

Please refer to the Virtex-5 Data sheet for a complete detailed summary of all device features.

All of the 440 available I/O on the Virtex-5 device are used in the design.

Depending on the availability of production silicon, the Virtex-5 LX Evaluation board may use engineering sample devices (CES1 or later). Please see the device errata on the Xilinx web page (<a href="www.xilinx.com">www.xilinx.com</a>) for any potential limitations these devices may have.

#### 2.2 LVDS Interface

The LVDS interface (J6 connector) is designed to support 10-bit TX and RX data transfers. 4 additional pairs are provided to be used as Frame and Clock if desired.

2.5V power is supplied through 8 pins of the LVDS connector.

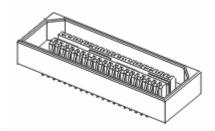

The connector used for the LVDS interface is manufactured by Samtec, PN: QSE-040-01-F-D-A. See figure 3 for a picture of the connector.

Figure 3 - LVDS connector - 80 pin

This connecter mates with a variety of other connector profiles. See the Samtec website (<a href="www.samtec.com">www.samtec.com</a>) for details on mating connectors.

See Table 3 for the LVDS pin assignments

| Signal Name | Virtex-5 Pin | Signal Name | Virtex-5 Pin |

|-------------|--------------|-------------|--------------|

| TX_CLK_P    | R21          | RX_CLK_P    | AB24         |

| TX_CLK_N    | R20          | RX_CLK_N    | AC24         |

| TX_FRAME_P  | U19          | RX_FRAME_P  | AD24         |

| TX_FRAME_N  | U20          | RX_FRAME_N  | AD23         |

| TX_DATA0_P  | T20          | RX_DATA0_P  | AE26         |

| TX_DATA0_N  | T19          | RX_DATA0_N  | AD26         |

| TX_DATA1_P  | AA20         | RX_DATA1_P  | AC21         |

| TX_DATA1_N  | AA19         | RX_DATA1_N  | AB21         |

| TX_DATA2_P  | AD19         | RX_DATA2_P  | AE25         |

| TX_DATA2_N  | AC19         | RX_DATA2_N  | AD25         |

| TX_DATA3_P  | AB20         | RX_DATA3_P  | W24          |

| TX_DATA3_N  | AB19         | RX_DATA3_N  | W23          |

| TX_DATA4_P  | V19          | RX_DATA4_P  | AA23         |

| TX_DATA4_N  | W19          | RX_DATA4_N  | AA24         |

| TX_DATA5_P  | AF23         | RX_DATA5_P  | AB22         |

| TX_DATA5_N  | AE23         | RX_DATA5_N  | AA22         |

| TX_DATA6_P  | Y21          | RX_DATA6_P  | V24          |

| TX_DATA6_N  | Y20          | RX_DATA6_N  | V23          |

| TX_DATA7_P  | V21          | RX_DATA7_P  | V21          |

| TX_DATA7_N  | V22          | RX_DATA7_N  | V22          |

| TX_DATA8_P  | Y23          | RX_DATA8_P  | U22          |

| TX_DATA8_N  | Y22          | RX_DATA8_N  | U21          |

| TX_DATA9_P  | W21          | RX_DATA9_P  | T23          |

| TX_DATA9_N  | W20          | RX_DATA9_N  | T22          |

Table 3 - Virtex-5 LVDS Pin Assignments

# 2.3 Memory

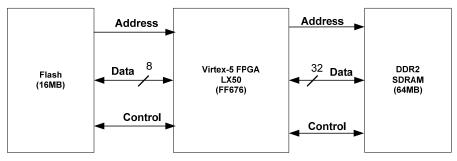

The Virtex-5 LX Evaluation board is populated with both high-speed RAM and non-volatile Flash to support various types of applications. The board has 64 Megabytes (MB) of DDR2 SDRAM and 16 MB of Flash. The following figure shows a high-level block diagram of the memory interfaces on the Evaluation board. If additional memory is necessary for Evaluation, check the Avnet Design Resource Center (DRC) for the availability of EXP compliant daughter cards with expansion memory (sold separately). Here is the link to the DRC web page: <a href="https://www.em.avnet.com/drc">www.em.avnet.com/drc</a>.

Figure 4 - Virtex-5 LX Evaluation Board Memory Interfaces

# 2.3.1 DDR2 SDRAM Interface

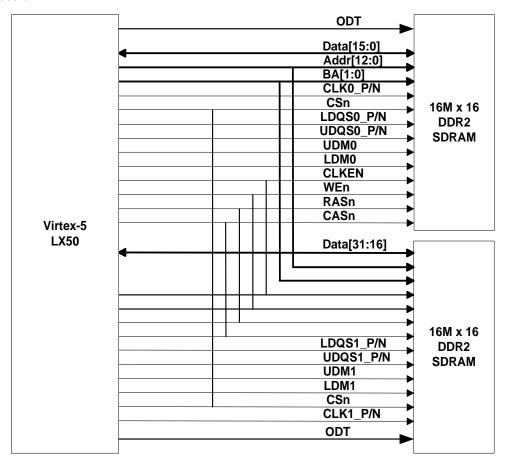

Two Micron DDR2 SDRAM devices, part number MT47H16M16BG-5E, make up the 32-bit data bus. Each device provides 32MB of memory on a single IC and is organized as 4 Megabits x 16 x 4 banks (256 Megabit). The device has an operating voltage of 1.8V and the interface is JEDEC Standard SSTL\_2 (Class I for unidirectional signals, Class II for bidirectional signals). The -5E speed grade supports 5 ns cycle times with a 3 clock read latency (DDR2-400). DDR2 On-Die-Termination (ODT) is also supported. The following figure shows a high-level block diagram of the DDR SDRAM interface on the V5LX Evaluation board.

Figure 5 - DDR2 SDRAM Interface

The following table provides timing and other information about the Micron device necessary to implement a DDR2 memory controller.

| MT47H16M16BG-5E: Timing Parameters            | Time (ps) or<br>Number |

|-----------------------------------------------|------------------------|

| Load Mode Register time (TMRD)                | 25000                  |

| Write Recovery time (TWR)                     | 15000                  |

| Write-to-Read Command Delay (TWTR)            | 1                      |

| Delay between ACT and PRE Commands (TRAS)     | 90000                  |

| Delay after ACT before another ACT (TRC)      | 65000                  |

| Delay after AUTOREFRESH Command (TRFC)        | 115000                 |

| Delay after ACT before READ/WRITE (TRCD)      | 25000                  |

| Delay after ACT before another row ACT (TRRD) | 15000                  |

| Delay after PRECHARGE Command (TRP)           | 20000                  |

| Refresh Command Interval (TREFC)              | 115000                 |

| Avg. Refresh Period (TREFI)                   | 7800000                |

| Memory Data Width (DWIDTH) (x2 devices)       | 32                     |

| Row Address Width (AWIDTH)                    | 13                     |

| Column Address Width (COL_AWIDTH)             | 9                      |

| Bank Address Width (BANK_AWIDTH)              | 2                      |

| Memory Range (64 MB total)                    | 0x3FFFFFF              |

**Table 4 - DDR2 SDRAM Timing Parameters**

The following guidelines were used in the design of the DDR2 interface to the Virtex-5 LX FPGA. These guidelines are based on Micron recommendations and board level simulation.

- Dedicated bus with matched trace lengths (+/- 100 mils)

- Memory clocks routed differentially

- 50 ohm\* controlled trace impedance

- · Series termination on bidirectional signals at the memory device

- Parallel termination following the memory device connection on all signals

- 100 ohm\* pull-up resistor to the termination supply on each branch of shared signals (control, address)

- · Termination supply that can both source and sink current

- Feedback clock routed with twice the length to simulate the total flight time

Some of the design considerations were specific to the Virtex-5 architecture. For example, the data strobe signals (DQS) were placed on Clock Capable I/O pins in order to support data capture techniques utilizing the SERDES function of the Virtex-5 I/O blocks. The appropriate DDR2 memory signals were placed in the clock regions that correspond to these particular Clock Capable I/O pins.

The DDR2 signals are connected to I/O Banks 15 and 16 of the Virtex-5 LX FPGA. The output supply pins (VCCO) for Banks 15 and 16 are connected to 1.8 Volts. This supply rail can be measured at test point TP3, which can be found in the area between the power modules and the can clock oscillator socket labeled "U5". The reference voltage pins (VREF) for Banks 15 and 16 are connected to the reference output of the National LP2997 DDR2 Termination Linear Regulator. This rail provides the voltage reference necessary for the SSTL\_2 I/O standard. The LP2997 regulator also provides the termination supply rail. The termination voltage is 0.9 Volts and can be measured at test point TP2, which can be found just above the can clock oscillator socket labeled "U5".

The following table contains the FPGA pin numbers for the DDR2 SDRAM interface.

<sup>\*</sup> Ideal impedance values. Actual may vary.

| Signal Name   | Virtex-5 pin | S  | Signal Name | Virtex-5 pin |

|---------------|--------------|----|-------------|--------------|

| DDR_A0        | B11          |    | DDR_D0      | B24          |

| DDR_A1        | A14          |    | DDR_D1      | D24          |

| DDR_A2        | C11          |    | DDR_D2      | B25          |

| DDR_A3        | A12          |    | DDR_D3      | C24          |

| DDR_A4        | C12          |    | DDR_D4      | C23          |

| DDR_A5        | B12          |    | DDR_D5      | A25          |

| DDR_A6        | B16          |    | DDR_D6      | D23          |

| DDR_A7        | C14          |    | DDR_D7      | A23          |

| DDR_A8        | B15          |    | DDR_D8      | C21          |

| DDR_A9        | B14          |    | DDR_D9      | B19          |

| DDR_A10       | A13          |    | DDR_D10     | D21          |

| DDR_A11       | A15          |    | DDR_D11     | C18          |

| DDR_A12       | C16          |    | DDR_D12     | D18          |

|               |              |    | DDR_D13     | C22          |

|               |              |    | DDR_D14     | D20          |

| DDR_BA0       | C13          |    | DDR_D15     | B21          |

| DDR_BA1       | D16          |    |             |              |

|               |              |    | DDR_D16     | B5           |

| DDR_CS#       | D10          |    | DDR_D17     | D5           |

| ODT           | C9           |    | DDR_D18     | A5           |

|               |              |    | DDR_D19     | C6           |

| DDR_WE#       | B17          |    | DDR_D20     | C7           |

| DDR_RAS#      | A10          |    | DDR_D21     | B6           |

| DDR_CAS#      | D11          |    | DDR_D22     | D6           |

| DDR_CLKEN     | A17          |    | DDR_D23     | A4           |

| DDR_LDM0      | A22          |    | DDR_D24     | A3           |

| DDR_UDM0      | A23          |    | DDR_D25     | C2           |

| DDR_LDM1      | A8           |    | DDR_D26     | C1           |

| DDR_UDM1      | A9           |    | DDR_D27     | D1           |

|               |              |    | DDR_D28     | C1           |

| DDR_LDQS0 P,N | A20, B20     |    | DDR_D29     | C4           |

| DDR_UDQS0 P,N | C19, D19     |    | DDR_D30     | C3           |

| DDR_LDQS1 P,N | D8, C8       |    | DDR_D31     | A2           |

| DDR_UDQS1 P,N | B7, A7       |    |             |              |

|               |              |    |             |              |

|               |              | DD | R_CLK_FB_O  | D3           |

|               |              | DE | DR_CLK_FB_I | AD18         |

Table 5 - Virtex-5 DDR2 FPGA Pinouts

Rev 1.3 01/02/2008 Literature # ADS-006204

#### 2.3.2 Flash Memory

The Virtex 5 LX Evaluation board has 16MB of non-volatile flash memory on board. The flash device is made by Intel, part number: PC28F128J3C120. The flash memory interface utilizes an 8-bit data bus and can be accessed directly without any external hardware settings or jumpers. See the following table for the flash memory to Virtex 5 pinout.

| Signal Name | Virtex-5 Pin | Signal Name | Virtex-5 Pin |

|-------------|--------------|-------------|--------------|

| FLASH_A0    | H8           | FLASH_A19   | G14          |

| FLASH_A1    | H9           | FLASH_A20   | AB17         |

| FLASH_A2    | H18          | FLASH_A21   | AA17         |

| FLASH_A3    | G19          | FLASH_A22   | AA8          |

| FLASH_A4    | G9           | FLASH_A23   | Y11          |

| FLASH_A5    | G10          | FLASH_A24   | Y10          |

| FLASH_A6    | G17          | FLASH_D0    | AA14         |

| FLASH_A7    | H17          | FLASH_D1    | AA13         |

| FLASH_A8    | G11          | FLASH_D2    | AB11         |

| FLASH_A9    | H11          | FLASH_D3    | AA12         |

| FLASH_A10   | H16          | FLASH_D4    | AB14         |

| FLASH_A11   | G16          | FLASH_D5    | AA15         |

| FLASH_A12   | H12          | FLASH_D6    | Y13          |

| FLASH_A13   | G12          | FLASH_D7    | Y12          |

| FLASH_A14   | G15          | FLASH_CE    | AA10         |

| FLASH_A15   | F15          | FLASH_OE    | AA9          |

| FLASH_A16   | H13          | FLASH_WE    | AB16         |

| FLASH_A17   | H14          | FLASH_RST   | F18          |

| FLASH_A18   | F13          |             |              |

Table 6 - Virtex-5 Flash Memory Pinout

#### 2.4 Clock Sources

The Virtex-5 LX Evaluation board includes all of the necessary clocks on the board to implement designs as well as providing the flexibility for the user to supply their own application specific clocks. The clock sources described in this section are used to derive the required clocks for the memory and communications devices, and the general system clocks for the logic design. This section also provides information on how to supply external user clocks to the FPGA via the on-board connectors and oscillator socket.

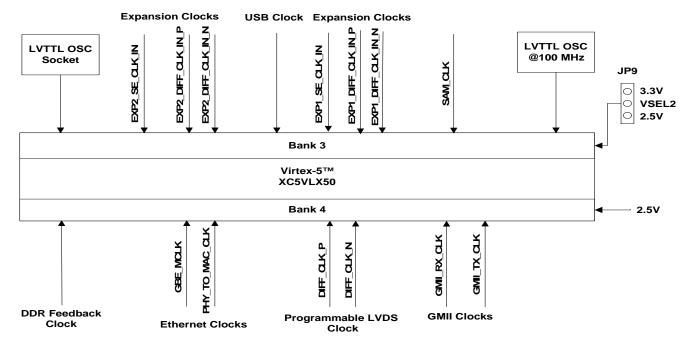

The following figure shows the clock nets connected to the I/O banks containing the global clock input pins on the Virtex-5 FPGA. Fifteen out of the twenty global clock inputs of the Virtex-5 FPGA are utilized on the board as clock resources. The other global clock inputs are used for user I/O. It should be noted that single-ended clock inputs must be connected to the P-side of the pin pair because a direct connection to the global clock tree only exists on this pin. The I/O voltages (VCCO) for Bank 3 are jumper selectable to either 2.5V or 3.3V. Bank 4 is fixed at 2.5V due the non-clock I/O that is connected to it being fixed at 2.5V. In order to use the differential clock inputs as LVDS inputs, the VCCO voltage for the corresponding bank must be set for 2.5V since the Virtex-5 FPGA does not support 3.3V differential signaling. Single-ended clock inputs do not have this restriction and may be either 2.5V or 3.3V. The interface clocks coming from 3.3V devices on the board are level-shifted to the appropriate VCCO voltage by CB3T standard logic devices prior to the Virtex-5 input pins.

Figure 6 - Clock Nets Connected to Global Clock Inputs

The on-board 100MHz oscillator provides the system clock input to the global clock tree. This single-ended, 100MHz clock can be used in conjunction with the Virtex-5 LX Digital Clock Managers (DCMs) to generate the various processor clocks and the clocks forwarded to the DDR SDRAM devices. The interface clocks supplied by the communications devices are derived from dedicated crystal oscillators.

| Reference# | Frequency | Derived Interface Clock | Derived Frequency | Virtex-5 pin# |

|------------|-----------|-------------------------|-------------------|---------------|

| U8         | 100 MHz   | CLK_100MHZ              | 100 MHz           | E18           |

| Y3         | 24 MHz    | USB_IFCLK               | 30, 48 MHz        | E10           |

| Y1         | 25 MHz    | CLK_SYNTH0_P/N          | 25 – 700 MHz      | AB10, AB9     |

| Y1         | 25 MHz    | CLK_SYNTH1_P/N          | 25 – 700 MHz      | AC23, AC22    |

|            |           | GMII_RX_CLK             | 2.5, 25 MHz       | AC8           |

| Y2         | 25 MHz    | GMII_TX_CLK             | 2.5, 25 MI        | AC17          |

|            |           | GBE_MCLK                | 125 MHz           | AD8           |

Table 7 - On-Board Clock Sources

In addition to the 100MHz oscillator, an 8-pin DIP clock socket is provided on the board so the user can supply their own oscillator of choice. The socket is a single-ended, LVTTL or LVCMOS compatible clock input to the FPGA that can be used as an alternate source for the system clock.

| Signal Name | Socket pin# |

|-------------|-------------|

| Enable      | 1           |

| GND         | 4           |

| Output      | 5           |

| VDD         | 8           |

Table 8 - Clock Socket "U5" Pin-out

| Net Name   | Input Type   | Connector.pin# | Virtex-5 pin# |

|------------|--------------|----------------|---------------|

| CLK_SOCKET | Global clock | U16.5          | E16           |

Table 9 - User Clock Input

Rev 1.3

01/02/2008 Literature # ADS-006204

# 2.4.1 ICS8442 Programmable LVDS Clock Synthesizer

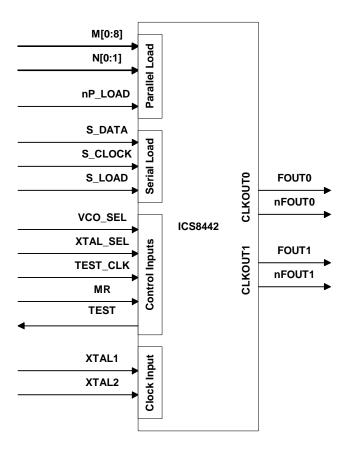

The Virtex-5 LX Evaluation board design uses the ICS8442 LVDS frequency synthesizer for generating various clock frequencies. A list of features included in the ICS8442 device is shown below.

• Output frequency range: 25MHz to 700MHz

RMS period jitter: 2.7ps (typical)

Cycle-to-cycle jitter: 27ps (typical)

Output rise and fall time: 650ps (maximum)

• Output duty cycle: 48/52

The following figure shows a high-level block diagram of the ICS8442 programmable LVDS clock synthesizer.

Figure 7 - ICS8442 Clock Synthesizer

| Signal Name    | Direction | Pull up/Pull down | Description                                                                                                                                                                                     |

|----------------|-----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M[0:4], M[6:8] | Input     | Pull down         | The M divider inputs, latched on the rising edge                                                                                                                                                |

| M[5]           | Input     | Pull up           | of the nP_LOAD signal.                                                                                                                                                                          |

| N[0:1]         | Input     | Pull down         | The N divider inputs, latched on the rising edge of the nP_LOAD signal.                                                                                                                         |

| TEST           | Output    |                   | The TEST output is active during the serial mode of operations. Please refer to the datasheet for more information.                                                                             |

| MR             | Input     | Pull down         | Active high reset signal.                                                                                                                                                                       |

| S_CLOCK        | Input     | Pull down         | Serial interface clock input. Data is shifted into the device on the rising edge of this clock.                                                                                                 |

| S_DATA         | Input     | Pull down         | Serial interface data input.                                                                                                                                                                    |

| S_LOAD         | Input     | Pull down         | Serial interface load signal. The contents of the serial data shift register is loaded into the internal dividers on the rising edge of this signal.                                            |

| TEST_CLK       | Input     | Pull down         | Test clock input.                                                                                                                                                                               |

| nP_LOAD        | Input     | Pull down         | The rising edge of this signal is used to load the M and N divider inputs into the device.                                                                                                      |

| XTAL1, XTAL2   | Input     |                   | Crystal clock input/output                                                                                                                                                                      |

| XTAL_SEL       | Input     | Pull up           | This signal is used to select between the crystal and the TEST_CLK input to the device. When this high, crystal is selected.                                                                    |

| VCO_SEL        | Input     | Pull up           | This signal is used to place the internal PLL in the bypass mode. When this signal is set to low, the PLL is placed in the bypass mode. For normal operations, this signal must be set to high. |

| FOUT0, FOUT1   | Output    |                   | Positive LVDS clock outputs                                                                                                                                                                     |

| nFOUT0, nFOUT1 | Output    |                   | Negative LVDS clock outputs                                                                                                                                                                     |

Table 10 - ICS8442 Clock Synthesizer Pin Description

The Input Clock Select signals of the ICS8442, "VCO\_SEL" and "XTAL\_SEL", are not used on the Virtex-5 LX Evaluation board. The internal pull-ups of these pins put the ICS8842 in normal operation mode where the 25 MHz crystal is used as the reference clock to generate the output clocks. None of the serial input control signals are connected on the board. Programming the ICS8442 device is only possible using the M/N DIP switches on the board.

# 2.4.1.1 ICS8442 Clock Generation

The ICS8442 output clocks are generated based on the following formula (assuming the crystal clock input is set to 25 MHz):

$$FOUT[0:1] = 25 \times M/N$$

Where 8 < M < 28 and N can take a value of 1, 2, 4, or 8. The variable M is determined by setting the binary number M[0:8] while N is set according to the following table:

| N[4.0] | N   | Output Clock Frequency | uency Range (MHz) |

|--------|-----|------------------------|-------------------|

| N[1:0] | l N | Minimum                | Maximum           |

| 00     | 1   | 200                    | 700               |

| 01     | 2   | 100                    | 350               |

| 10     | 4   | 50                     | 175               |

| 11     | 8   | 25                     | 87.5              |

Table 11 - ICS8442 N Settings

For example, to generate a 62.5 MHz clock, N[1:0] will be set to "10" (it can also be set to "11" since either one will be the correct frequency range for the 62.5 MHz clock) and M will be set to "000001010" (decimal 10). So, from the above formula:

The following table shows how the M and N values can be set to generate a clock source for a few common applications. All the values for M and N are based on the 25MHz crystal clock input to the ICS8442 device. A complete list of frequencies generated by the ICS8442 (based on a 25MHz input clock) is provided in the following sections.

| Interconnect     | FOUT0 and   | ICS8442 M and N Settings |    |    |    |    |    |    |    |    |    |    |

|------------------|-------------|--------------------------|----|----|----|----|----|----|----|----|----|----|

| Technology       | FOUT1 (MHz) | M8                       | M7 | М6 | M5 | M4 | М3 | M2 | M1 | M0 | N1 | N0 |

| Gigabit Ethernet | 125         | 0                        | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 1  |

Table 12 - Example of the ICS8442 M and N Settings

# 2.4.1.2 ICS8442 Programming Mode

The Virtex-5 LX Evaluation board allows programming of the M and N values in parallel mode. In parallel mode, M and N values are programmed into the device when the nP\_LOAD signal pulses low. Please refer to the ICS8442 datasheet for more information on programming modes of loading the M and N values into the device.

# 2.4.1.3 ICS8442 M and N Settings

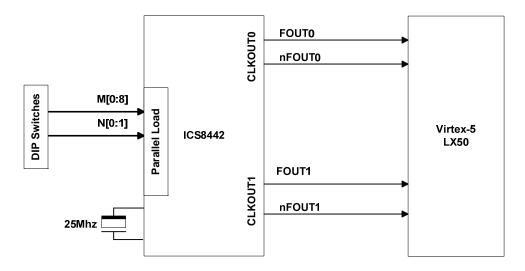

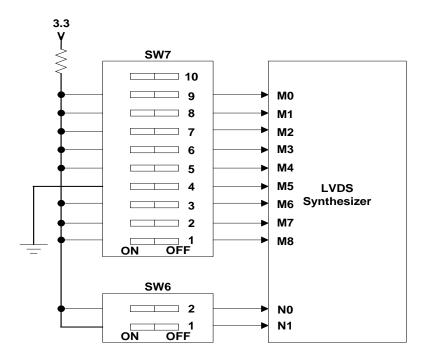

The following figure shows how the ICS8442 programmable LVDS clock synthesizer is used on the Virtex-5 LX Evaluation board. To limit the number of required Virtex-5 I/O pins, only Parallel Mode is supported. DIP switches are provided on the board for the manual setting of the M and N values for the ICS8442.

Figure 8 - ICS8442 Clock Synthesizer Interface to the FPGA

As shown in the above figure, the ICS8442 device outputs two identical LVDS clock sources. One of these clock sources (CLKOUT0) is routed to a global clock pin on Bank 4 of the Virtex-5. The other is routed to Bank 17 and is connected to a clock capable pin. These types of clock pins are not global, but "regional". Unlike global clocks, the span of a regional clock signal is limited to three clock regions. These networks are especially useful for source-synchronous interface designs. The Virtex-5 I/O banks are the same size as a clock region. Refer to the Virtex-5 User Guide for a detailed explanation of how regional clocking works and how it is implemented.

The following tables show the DIP switch settings for M and N selections. Please refer to Table 9 for the information on pull-up and pull-down resistors provided internal to the ICS8442 device for the M and N input signals.

Figure 9 - M and N DIP Switches for the LVDS Synthesizer

|       |        | Switch | Position   |

|-------|--------|--------|------------|

| SW7   | M[8:0] | OFF    | ON         |

| DIP1  | M8     | 0      | 1          |

| DIP2  | M7     | 0      | 1          |

| DIP3  | M6     | 0      | 1          |

| DIP4  | M5     | 1      | 0 Note (1) |

| DIP5  | M4     | 0      | 1          |

| DIP6  | M3     | 0      | 1          |

| DIP7  | M2     | 0      | 1          |

| DIP8  | M1     | 0      | 1          |

| DIP9  | M0     | 0      | 1          |

| DIP10 | Unused | NA     | NA         |

Note(1) – The polarity of M5 (DIP4) is the opposite of all other DIP switch positions.

Table 13 - DIP Switch Setting for M[8:0]

|      |        | Switch Position |    |

|------|--------|-----------------|----|

| SW6  | N[1:0] | OFF             | ON |

| DIP1 | N1     | 0               | 1  |

| DIP2 | N0     | 0               | 1  |

Table 14 - DIP Switch Setting for N[1:0]

01/02/2008

The following table shows a complete list of frequencies generated by the ICS8442 device based on a 25MHz crystal reference clock input.

| M[8:0]    | N[1:0] | FOUT[1:0] (MHz) | M[8:0]    | N[1:0] | FOUT[1:0] (MHz) |

|-----------|--------|-----------------|-----------|--------|-----------------|

| 000001000 | 11     | 25 (Min)        | 000011000 | 10     | 150             |

| 000001001 | 11     | 28.125          | 000011001 | 10     | 156.25          |

| 000001010 | 11     | 31.25           | 000001101 | 01     | 162.5           |

| 000001011 | 11     | 34.375          | 000011010 | 10     | 162.5           |

| 000001100 | 11     | 37.5            | 000011011 | 10     | 168.75          |

| 000001101 | 11     | 40.625          | 000001110 | 01     | 175             |

| 000001110 | 11     | 43.75           | 000011100 | 10     | 175             |

| 000001111 | 11     | 46.875          | 000001111 | 01     | 187.5           |

| 000001000 | 10     | 50              | 000001000 | 00     | 200             |

| 000010000 | 11     | 50              | 000010000 | 01     | 200             |

| 000010001 | 11     | 53.125          | 000010001 | 01     | 212.5           |

| 000001001 | 10     | 56.25           | 000001001 | 00     | 225             |

| 000010010 | 11     | 56.25           | 000010010 | 01     | 225             |

| 000010011 | 11     | 59.375          | 000010011 | 01     | 237.5           |

| 000001010 | 10     | 62.5            | 000001010 | 00     | 250             |

| 000010100 | 11     | 62.5            | 000010100 | 01     | 250             |

| 000010101 | 11     | 65.625          | 000010101 | 01     | 262.5           |

| 000001011 | 10     | 68.75           | 000001011 | 00     | 275             |

| 000010110 | 11     | 68.75           | 000010110 | 01     | 275             |

| 000010111 | 11     | 71.875          | 000010111 | 01     | 287.5           |

| 000001100 | 10     | 75              | 000001100 | 00     | 300             |

| 000011000 | 11     | 75              | 000011000 | 01     | 300             |

| 000011001 | 11     | 78.125          | 000011001 | 01     | 312.5           |

| 000001101 | 10     | 81.25           | 000001101 | 00     | 325             |

| 000011010 | 11     | 81.25           | 000011010 | 01     | 325             |

| 000011011 | 11     | 84.375          | 000011011 | 01     | 337.5           |

| 000001110 | 10     | 87.5            | 000001110 | 00     | 350             |

| 000011100 | 11     | 87.5            | 000011100 | 01     | 350             |

| 000001111 | 10     | 93.75           | 000001111 | 00     | 375             |

| 000001000 | 01     | 100             | 000010000 | 00     | 400             |

| 000010000 | 10     | 100             | 000010001 | 00     | 425             |

| 000010001 | 10     | 106.25          | 000010010 | 00     | 450             |

| 000001001 | 01     | 112.5           | 000010011 | 00     | 475             |

| 000010010 | 10     | 112.5           | 000010100 | 00     | 500             |

| 000010011 | 10     | 118.75          | 000010101 | 00     | 525             |

| 000001010 | 01     | 125             | 000010110 | 00     | 550             |

| 000010100 | 10     | 125             | 000010111 | 00     | 575             |

| 000010101 | 10     | 131.25          | 000011000 | 00     | 600             |

| 000001011 | 01     | 137.5           | 000011001 | 00     | 625             |

| 000010110 | 10     | 137.5           | 000011010 | 00     | 650             |

| 000010111 | 10     | 143.75          | 000011011 | 00     | 675             |

| 000001100 | 01     | 150             | 000011100 | 00     | 700 (Max)       |

Table 15 - Synthesizer Clock Outputs for M and N Values

The following table shows the Virtex-5 pin connections for the two differential clock outputs of the synthesizer.

| Net Name     | I/O Type    | Virtex-5 pin |

|--------------|-------------|--------------|

| DIFF_CLK_0_P | FPGA input  | AB10         |

| DIFF_CLK_0_N | FFGA Iliput | AB9          |

| DIFF_CLK_1_P | EDC A input | AC23         |

| DIFF_CLK_1_N | FPGA input  | AC22         |

Table 16 - ICS8442 Pin Assignments

#### 2.5 Communication

The Virtex-5 LX FPGA has access to Ethernet, USB and RS232 physical layer transceivers for communication purposes. Network access is provided by a 10/100/1000 Mb/s Ethernet PHY, which is connected to the Virtex-5 via a standard GMII interface. The PHY connects to the outside world with a standard RJ45 connector (J7) and is located in the lower right corner of the board. General purpose I/O transfers are supported by way of the USB 2.0 port. The USB Type B peripheral connector (JR1) is mounted on the board in the lower left corner of the board. Serial port communication to the embedded processor or FPGA fabric is provided through a dual-channel RS232 transceiver.

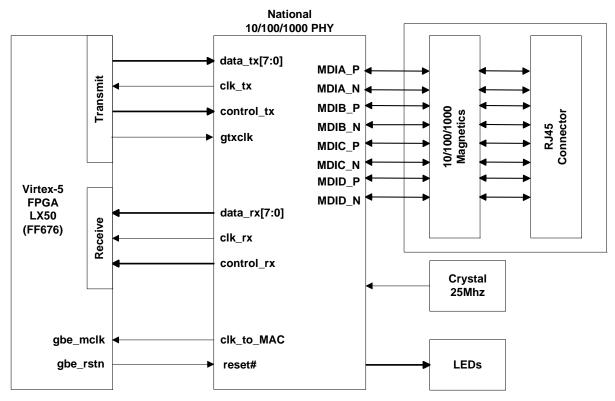

# 2.5.1.1 10/100/1000 Ethernet PHY

The PHY is a National DP83865DVH Gig PHYTER® V. The DP83865 is a low power version of National's Gig PHYTER V with a 1.8V core voltage and 2.5V I/O voltage. The PHY also supports 3.3V I/O, but the 2.5V option is used on the board. The PHY is connected to a Tyco RJ-45 jack with integrated magnetics (part number: 1-6605833-1). The jack also integrates two LEDs and their corresponding resistors as well as several other passive components. External logic is used to logically OR the three link indicators for 10, 100 and 1000 Mb/s to drive a Link LED on the RJ-45 jack. The external logic is for the default strap options and may not work if the strap options are changed. Four more LEDs are provided on the board for status indication. These LEDs indicate Link at 10 Mb/s, Link at 100 Mb/s, Link at 1000 Mb/s and Full Duplex operation. The PHY clock is generated from its own 25 MHz crystal. The following figure shows a high-level block diagram of the interface to the DP83865 Tri-mode Ethernet PHY.

Figure 10 - 10/100/1000 Mb/s Ethernet Interface

The PHY address is set to 0b00001 by default. PHY address 0b00000 is reserved for a test mode and should not be used. Three-pad resistor jumpers are used to set the strapping options. These jumper pads provide the user with the ability to change the settings by moving the resistors. The strapping options are shown in the following table. The dual-function pins that are used for both a strapping option and to drive an LED, have a set of two jumpers per pin. The dual-function pins are indicated by an asterisk in the table.

| Function                | Jumper Installation | Resistor | Mode Enabled                                      |

|-------------------------|---------------------|----------|---------------------------------------------------|

|                         | JT13: pins 1-2      | 0 ohm    | Auto-negotiation enabled (default)                |

| Auto-Negotiation*       | JT14: pins 1-2      | 0 ohm    | Auto-negotiation enabled (default)                |

| Auto-Negotiation        | JT13: pins 2-3      | 0 ohm    | Auto-negotiation disabled                         |

|                         | JT14: pins 2-3      | 0 ohm    | Auto-negotiation disabled                         |

|                         | JT15: pins 1-2      | 0 ohm    | Full Duplex (default)                             |

| Full/Half Duplex*       | JT16: pins 1-2      | 0 ohm    | Tuli Duplex (deladit)                             |

| T dil/Tidil Duplex      | JT15: pins 2-3      | 0 ohm    | Half Duplex                                       |

|                         | JT16: pins 2-3      | 0 ohm    | Tian Buplox                                       |

|                         | JT17: pins 1-2      |          | Speed Selection: (Auto-Neg enabled)               |

| Cn and 4*               | JT18: pins 1-2      | 0 ohm    | Speed1 Speed0 Speed Advertised                    |

| Speed 1*                | •                   | 0 ohm    | 1 1 1000BASE-T, 10BASE-T                          |

|                         | (Speed1 - 0)        |          | 1 0 1000BASE-T                                    |

|                         | JT11: pins 1-2      |          | 0 1 1000BASE-T, 100BASE-TX                        |

|                         | JT12: pins 1-2      | 0 ohm    | 0 0 1000BASE-T, 100BASE-TX, 10BASE-T              |

| Speed 0*                | 01121 pino 12       | 0 ohm    |                                                   |

|                         | (Speed0 - 0)        | 0 0      | Default: 1000BASE-T, 100BASE-TX, 10BASE-T         |

|                         | JT9: pins 1-2       | 0 ohm    | DINA III OLOGODA (II ( II)                        |

| DLIV address 0*         | JT10: pins 1-2      | 0 ohm    | PHY Address 0b00001 (default)                     |

| PHY address 0*          | JT9: pins 2-3       | 0 ohm    | DLIV Address 0500000                              |

|                         | JT10: pins 2-3      | 0 ohm    | PHY Address 0b00000                               |

| Non-IEEE Compliant Mode | JT3: pins 1-2       | 1 K      | Compliant and Non-comp. Operation (default)       |

| Non-ieee Compliant wode | JT3: pins 2-3       | 1 K      | Inhibits Non-compliant operation                  |

| Manual MDIX Setting     | JT4: pins 1-2       | 1 K      | Straight Mode (default)                           |

| Maridal MDIX Setting    | JT4 pins 2-3        | 1 K      | Cross-over Mode                                   |

| Auto MDIX Enable        | JT7: pins 1-2       | 1 K      | Automatic Pair Swap – MDIX (default)              |

| Auto MDIA Ellable       | JT7: pins 2-3       | 1 K      | Set to manual preset – Manual MDIX Setting (JT12) |

| Multiple Node Enable    | JT6: pins 1-2       | 1 K      | Single node – NIC (default)                       |

| wulliple Node Ellable   | JT6: pins 2-3       | 1 K      | Multiple node priority – switch/hub               |

| Clock to MAC Enable     | JT8: pins 1-2       | 1 K      | CLK_TO_MAC output enabled (default)               |

| CIOCK TO WIAC ETIABLE   | JT8: pins 2-3       | 1 K      | CLK_TO_MAC output disabled                        |

**Table 17 - Ethernet PHY Hardware Strapping Options**

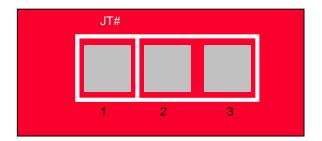

The default options as indicated in Table 23 are Auto-Negotiation enabled, Full Duplex mode, Speed advertised as 10/100/1000 Mb/s, PHY address 0b00001, IEEE Compliant and Non-compliant support, straight cable in non-MDIX mode, auto-MDIX mode enabled, Single node (NIC) and CLK\_TO\_MAC enabled. The pin-out for a jumper pad is shown below.

The auto-MDIX mode provides automatic swapping of the differential pairs. This allows the PHY to work with either a straight-through cable or crossover cable. Use a CAT-5e or CAT-6 Ethernet cable when operating at 1000 Mb/s (Gigabit Ethernet). The boundary-scan Test Access Port (TAP) controller of the DP83865 must be in reset for normal operation. This active low reset pin of the TAP (TRST) is pulled low through a 1K resistor on the board. The following table provides the Virtex-5 pin assignments for the Ethernet PHY interface.

| Net Name     | Virtex-5 pin | Net Name    | Virtex-5 pin |

|--------------|--------------|-------------|--------------|

| GBE_MDC      | AE7          | GBE_INT#    | AF8          |

| GBE_MDIO     | AF7          | GBE_RST#    | AC14         |

| GBE_MCLK     | AD15         | GMII_CRS    | AE13         |

| GMII_GTC_CLK | AD8          | GMII_COL    | AC13         |

| GMII_TXD0    | AD16         | GMII_RXD0   | AE8          |

| GMII_TXD1    | AE16         | GMII_RXD1   | AF9          |

| GMII_TXD2    | AE15         | GMII_RXD2   | AD9          |

| GMII_TXD3    | AF15         | GMII_RXD3   | AF10         |

| GMII_TXD4    | AF13         | GMII_RXD4   | AE10         |

| GMII_TXD5    | AF14         | GMII_RXD5   | AE11         |

| GMII_TXD6    | AD13         | GMII_RXD6   | AC11         |

| GMII_TXD7    | AC7          | GMII_RXD7   | AF12         |

| GMII_TX_EN   | AF17         | GMII_RX_DV  | AE12         |

| GMII_TX_ER   | AE17         | GMII_RX_ER  | AB12         |

| GMII_TX_CLK  | AC17         | GMII_RX_CLK | AC8          |

Table 18 - Ethernet PHY Pin Assignments

# 2.5.1.2 Universal Serial Bus (USB)

The Virtex-5 LX Evaluation Board includes a Cypress EZ-USB FX2™ USB Microcontroller, part number CY7C68013A-100AC. The EZ-USB FX2 device is a single-chip integrated USB 2.0 transceiver, Serial Interface Engine (SIE) and 8051 microcontroller. This device supports full-speed (12 Mbps) and high-speed (480 Mbps) modes, but does not support low-speed mode (1.5 Mbps). The FX2 interface to the Virtex-5 FPGA is a programmable state machine that supports 8- or 16-bit parallel data transfers. This interface is called the General Programmable Interface (GPIF). The GPIF is controlled by Waveform Descriptors that are created with the Cypress "GPIFTool" utility and downloaded to the FX2 over the USB cable. The GPIF descriptors are stored in internal RAM and are loaded by the firmware during initialization. The GPIF interface is made up of the signals in the following table, which are connected to Virtex-5 FPGA. The USB FX2 device can also be used in a slave mode where the FPGA accesses the FX2 like a FIFO. For more information about the FX2 modes of operation, see the "EZ-USB FX2 Technical Reference Manual" and the FX2 datasheet available on Cypress Semiconductor's web site (http://www.cypress.com).

Some of the additional GPIF pins are connected to the SelectMAP configuration port on the Virtex-5 FPGA. Avnet has designed a Windows utility program that can utilize this connection to the SelectMAP port to update the FPGA configuration over the USB port. The additional pins used for the SelectMAP interface are shaded in the table. The Virtex-5 LX Evaluation board should be used with version 3.3 or later of the "ADS USB Utility". This program can be downloaded from the Design Resource Center (<a href="https://www.em.avnet.com/drc">www.em.avnet.com/drc</a>). Remove all three of the jumpers on JP22 (Mode jumpers) to enable the USB Utility to configure the Virtex-5 device. Then place a jumper on JP16 "FPGA\_CFG\_OE". The USB Utility only supports bit files generated with CCLK as the start-up clock.

It is important to note that the lower 8 bits of the USB data bus tied to the SelectMap data port of the Virtex-5 FPGA are shared with the on-board FLASH. The data is controlled via two 4-bit muxes. The OE of the muxes is controlled by some external decode logic (U16, U17, U50, and U51). The decode logic detects when the proper configuration mode for USB is selected and enables the mux's outputs. The USB device drives the mode pins during USB configuration, so it is important to remove all mode jumper pins if configuring the Virtex-5 FPGA via the USB utility. JP16 ("FPGA\_CFG\_OE") enables the switch on the muxes to allow USB data to pass to the Virtex-5 FPGA. This jumper must be installed to allow FPGA configuration via USB.

| OTL fol      | LIOD OTLO    | 1 T 10 | 0 + 1 + 1 0                                  |

|--------------|--------------|--------|----------------------------------------------|

| CTL[0]       | USB_CTL0     | AF18   | Control output or Slave-FIFO Flag A (Level#) |

| CTL[1]       | USB_CTL1     | AC9    | Control output or Slave-FIFO Flag B (Full#)  |

| CTL[2]       | USB_CTL2     | AC16   | Control output or Slave-FIFO Flag C (Empty#) |

| CTL[3]       | CTL3_PROG#   | -      | Output enable for FPGA_PROG# driver          |

| CTL[4]       | CTL4_CS#     | -      | SelectMAP chip select when JP13 installed    |

| CTL[5]       | CTL5_RDWR#   | -      | SelectMAP write enable when JP13 installed   |

| RDY[0]       | USB_RDY0     | AF19   | Sample-able ready inputs                     |

| RDY[1]       | USB_RDY1     | AC18   | Odmpie able ready inputs                     |

| RDY[2]       | FPGA_BUSY    | -      | SelectMAP port busy indication               |

| RDY[3]       | FPGA_DONE    | -      | FPGA configuration DONE pin                  |

| RDY[4]       | FPGA_INIT#   | -      | FPGA initialization pin                      |

| FD[0]        | USB_FD0 (D0) | -      | Bidirectional FIFO data bus (also SMAP data) |

| FD[1]        | USB_FD1 (D1) | -      | 1                                            |

| FD[2]        | USB_FD2 (D2) | -      | **************************************       |

| FD[3]        | USB_FD3 (D3) | -      | These Data pins are muxed through U14 and    |

| FD[4]        | USB_FD4 (D4) | -      | U15. All Mode jumpers (JP22) must be         |

| FD[5]        | USB_FD5 (D5) | 1 -    | removed and JP16 installed to allow data to  |

| FD[6]        | USB_FD6 (D6) | 1-     | pass through to the FPGA. This is true for   |

| FD[7]        | USB_FD7 (D7) | -      | both configuration and normal operation.     |

| FD[8]        | USB FD8      | AE22   | Bidirectional FIFO data bus                  |

| FD[9]        | USB_FD9      | AD21   | Dianocional i ii o data bac                  |

| FD[10]       | USB_FD10     | AF22   |                                              |

| FD[11]       | USB_FD11     | AD20   |                                              |

| FD[12]       | USB_FD12     | AE21   | -                                            |

|              | USB_FD13     | AE20   | -                                            |

| FD[13]       |              |        | -                                            |

| FD[14]       | USB_FD14     | AF20   | _                                            |

| FD[15]       | USB_FD15     | AE18   | 0 : 15004 0011( : 170 1 :                    |

| GPIFADR[0]   | USB_PC0      | -      | Optional FPGA_CCLK out – see JT6 selection   |

| GPIFADR[1]   | FPGA_M2      | -      | SelectMAP port mode - M2                     |

| GPIFADR[2]   | FPGA_M1      | -      | SelectMAP port mode - M1                     |

| GPIFADR[3]   | FPGA_M0      | -      | SelectMAP port mode - M0                     |

| GPIFADR[4]   | JTAG_TDI     | -      | Optional JTAG interface – TDI (install RP1)  |

| GPIFADR[5]   | JTAG_TDO     | -      | Optional JTAG interface – TDO (install RP1)  |

| GPIFADR[6]   | JTAG_TMS     | -      | Optional JTAG interface – TMS (install RP1)  |

| GPIFADR[7]   | JTAG_TCK     | -      | Optional JTAG interface – TCK (install RP1)  |

| IFCLK        | USB_IFCLK    | E10    | Interface clock, optional FPGA_CCLK (JT6)    |

|              |              |        |                                              |

| PA0/INT0#    | USB_INT0#    | AD11   | Port A I/O or active-low interrupt 0         |

| PA1/INT1#    | USB_INT1#    | AD10   | Port A I/O or active-low interrupt 1         |

| PA2/SLOE     | USB_SLOE     | Y8     | Port A I/O or slave-FIFO output enable       |

| PA3/WU2      | USB_WU2      | AB16   | Port A I/O or alternate wake-up pin          |

| PA4/FIFOADR0 | USB_FA0      | AA18   | Port A I/O or slave-FIFO address select 0    |

| PA5/FIFOADR1 | USB_FA1      | Y18    | Port A I/O or slave-FIFO address select 1    |

| PA6/PKTEND   | USB_PEND     | AD14   | Port A I/O or slave-FIFO packet end          |

| PA7/SLCS#    | USB_SLCS#    | AC12   | Port A I/O or slave-FIFO enable              |

| RESET#       | USB_RST#     | AC12   | USB device active-low reset                  |

| NESEI#       | U3D_R31#     | AU14   | OOD device active-low reset                  |

Virtex-5 pin

Description

Table 19 - USB Interface FPGA Pin-out

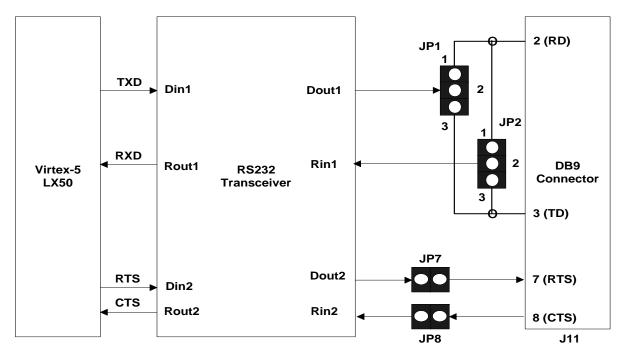

# 2.5.1.3 RS232

**FX2 Signal**

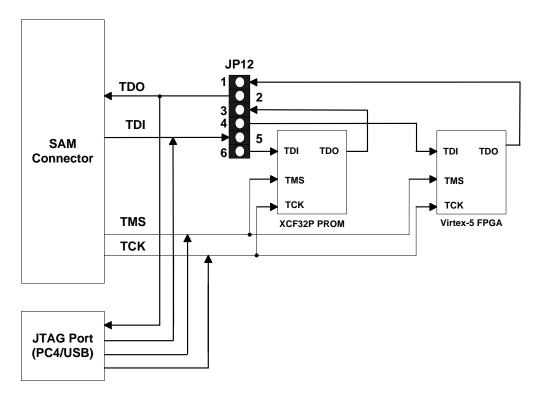

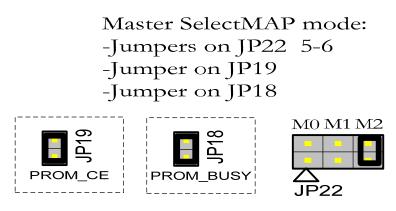

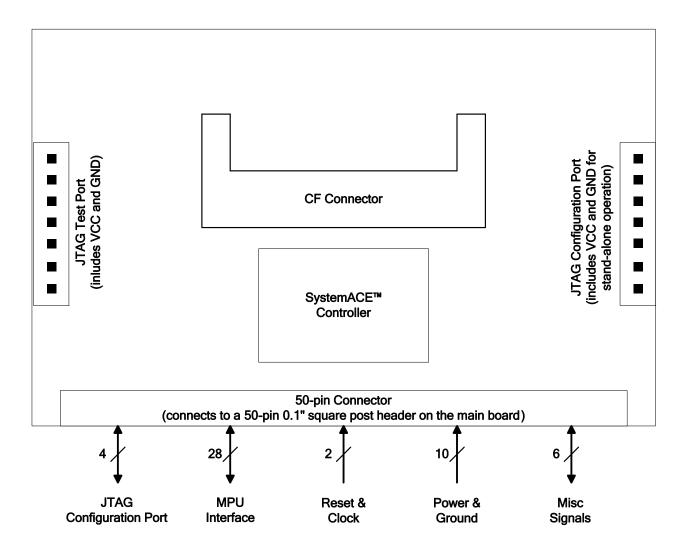

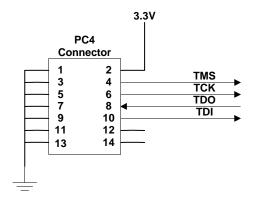

**Net Name**